# 8-BIT MICROCONTROLLER New 8FX MB95810K Series HARDWARE MANUAL

# 8-BIT MICROCONTROLLER New 8FX MB95810K Series HARDWARE MANUAL

For the information for microcontroller supports, see the following website.

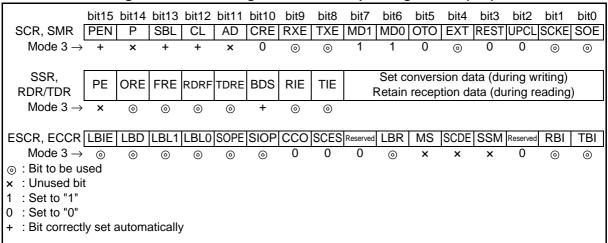

http://edevice.fujitsu.com/micom/en-support/

**FUJITSU SEMICONDUCTOR LIMITED**

# **PREFACE**

## **■** The Purpose and Intended Readership of This Manual

Thank you very much for your continued special support for Fujitsu Semiconductor products.

The MB95810K Series is a line of products developed as general-purpose products in the New 8FX family of proprietary 8-bit single-chip microcontrollers applicable as application-specific integrated circuits (ASICs). The MB95810K Series can be used for a wide range of applications from consumer products including portable devices to industrial equipment.

Intended for engineers who actually develop products using the MB95810K Series of microcontrollers, this manual describes its functions, features, and operations. You should read through the manual.

For details on individual instructions, refer to "F<sup>2</sup>MC-8FX Programming Manual".

This manual is written to explain the respective configurations and operations of peripheral functions, but not to provide specifications of a device.

For detailed specifications of a device, refer to its data sheet.

Note: F<sup>2</sup>MC is the abbreviation of FUJITSU Flexible Microcontroller.

#### ■ Trademark

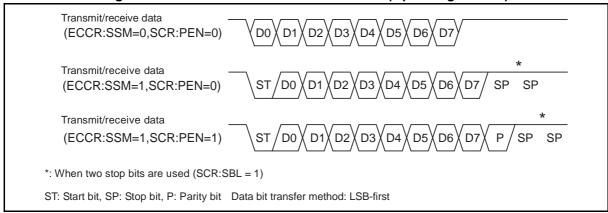

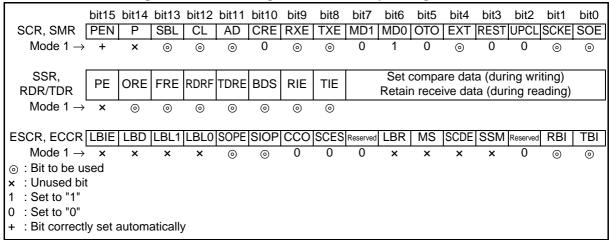

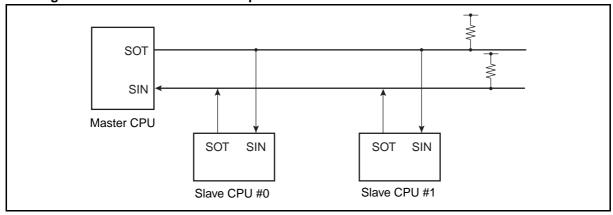

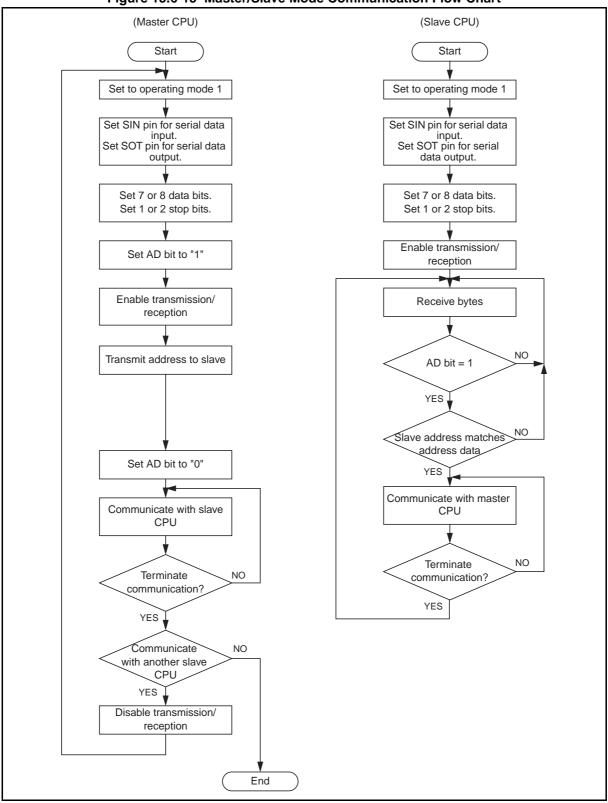

The company names and brand names in this document are the trademarks or registered trademarks of their respective owners.

# **■** Sample Programs

Fujitsu Semiconductor provides sample programs free of charge to operate the peripheral functions of the New 8FX family of microcontrollers. Feel free to use such sample programs to check the operational specifications and usages of Fujitsu microcontrollers.

Note that sample programs are subject to change without notice. As these pieces of software are offered to show standard operations and usages, evaluate them sufficiently before use with your system. Fujitsu Semiconductor assumes no liability for any damages whatsoever arising out of the use of sample programs.

# **How to Use This Manual**

# **■** Finding a function

The following methods can be used to search for details of a peripheral function in this manual:

• Searching from CONTENTS

CONTENTS lists the contents in this manual in the order of description.

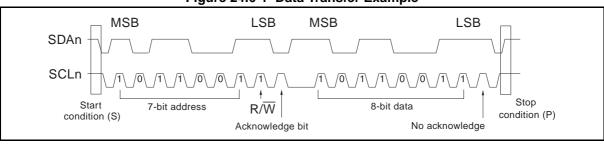

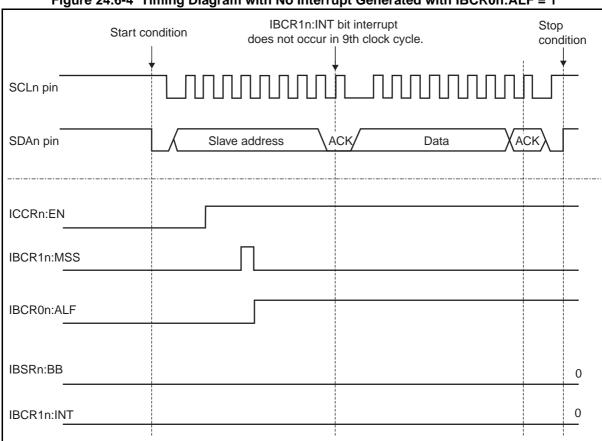

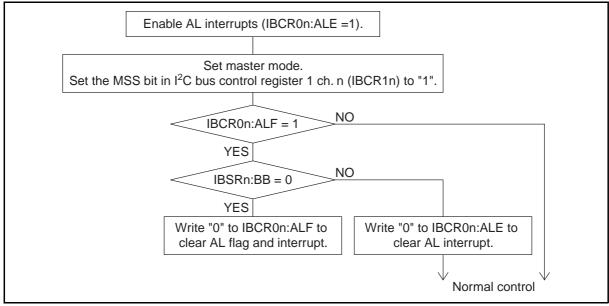

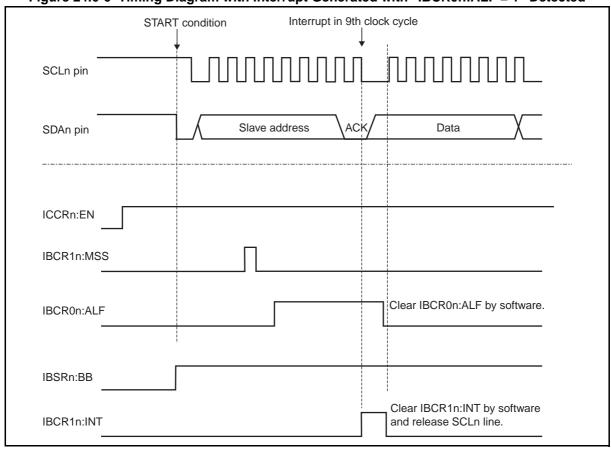

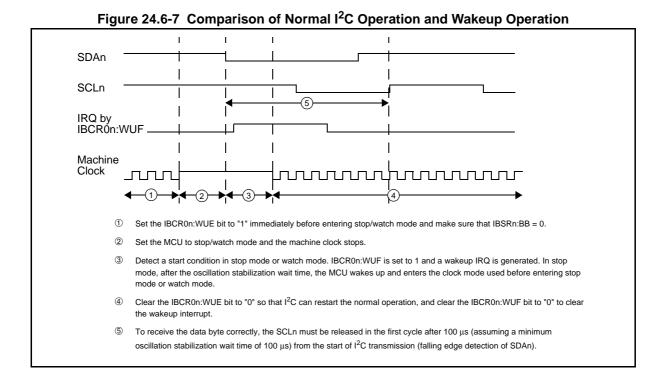

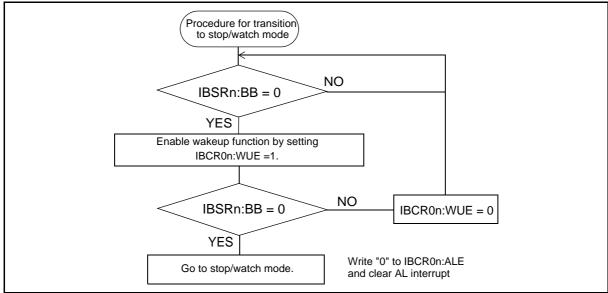

Searching from registers

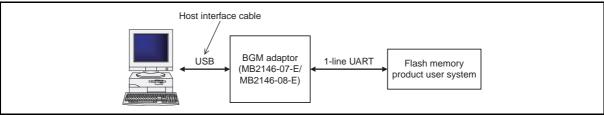

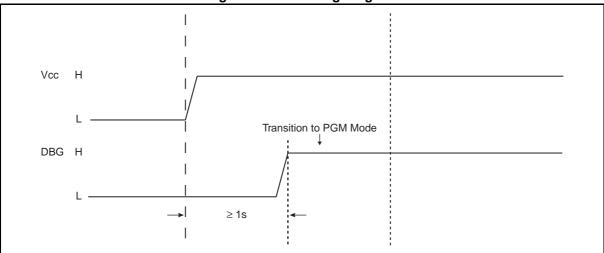

The address at which a register is located is not mentioned in this manual. To check the address of a register, refer to "I/O MAP" in the device data sheet.

# ■ Chapters

This manual explains one peripheral function in one chapter.

# **■** Terminology

This manual uses the following terminology.

| Term | Explanation                             |

|------|-----------------------------------------|

| Word | Indicates an access in unit of 16 bits. |

| Byte | Indicates an access in unit of 8 bits.  |

#### ■ Notations

The notations in "■ Register Configuration" in this manual are explained below:

- bit: bit number

- · Field: bit field name

- Attribute: Attributes for read access and write access of each bit

- R: Read-only

- W: Write-only

- R/W: Readable/Writable

- —: Undefined

- Initial value: Initial value of a bit after a reset

- 0: The initial value is "0".

- 1: The initial value is "1".

- X: The initial value is undefined.

Multiple bits are indicated in this manual in the following way.

- Example 1: bit7:0 represents bit7 to bit0.

- Example 2: SCM[2:0] represents SCM2 to SCM0.

The values such as those indicating addresses are written in this manual in the following ways:

- Hexadecimal number: The prefix "0x" is attached to the beginning of a value (e.g.: 0xFFFF).

- Binary number: The prefix "0b" is attached to the beginning of a value (e.g.: 0b1111).

- Decimal number: Only the number is used (e.g.: 1234).

In this manual, "n" in a pin name and a register abbreviation represents the channel number.

- The contents of this document are subject to change without notice.

Customers are advised to consult with sales representatives before ordering.

- The information, such as descriptions of function and application circuit examples, in this document are presented solely for the purpose of reference to show examples of operations and uses of FUJITSU SEMICONDUCTOR device; FUJITSU SEMICONDUCTOR does not warrant proper operation of the device with respect to use based on such information. When you develop equipment incorporating the device based on such information, you must assume any responsibility arising out of such use of the information. FUJITSU SEMICONDUCTOR assumes no liability for any damages whatsoever arising out of the use of the information.

- Any information in this document, including descriptions of function and schematic diagrams, shall not be

construed as license of the use or exercise of any intellectual property right, such as patent right or copyright, or

any other right of FUJITSU SEMICONDUCTOR or any third party or does FUJITSU SEMICONDUCTOR

warrant non-infringement of any third-party's intellectual property right or other right by using such information.

FUJITSU SEMICONDUCTOR assumes no liability for any infringement of the intellectual property rights or other

rights of third parties which would result from the use of information contained herein.

- The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite). Please note that FUJITSU SEMICONDUCTOR will not be liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products.

- Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss

from such failures by incorporating safety design measures into your facility and equipment such as redundancy,

fire protection, and prevention of over-current levels and other abnormal operating conditions.

- Exportation/release of any products described in this document may require necessary procedures in accordance with the regulations of the Foreign Exchange and Foreign Trade Control Law of Japan and/or US export control laws

- The company names and brand names herein are the trademarks or registered trademarks of their respective owners.

Copyright © 2012 FUJITSU SEMICONDUCTOR LIMITED All rights reserved.

# **CONTENTS**

| CHAPTI  | ER 1 MEMORY ACCESS MODE                                 | 1  |

|---------|---------------------------------------------------------|----|

| 1.1     | Memory Access Mode                                      | 2  |

| CLIADTI | ED 2 CDU                                                | 2  |

| CHAPTI  |                                                         |    |

| 2.1     | Dedicated Registers                                     |    |

| 2.1.1   | 9 ( )                                                   |    |

| 2.1.2   |                                                         |    |

| 2.1.3   | 3 ( ,                                                   |    |

| 2.2     | General-purpose Register                                |    |

| 2.3     | Placement of 16-bit Data in Memory                      | 13 |

| CHAPTI  | ER 3 CLOCK CONTROLLER                                   | 15 |

| 3.1     | Overview                                                | 16 |

| 3.2     | Oscillation Stabilization Wait Time                     | 24 |

| 3.3     | Registers                                               | 27 |

| 3.3.1   | _                                                       |    |

| 3.3.2   | PLL Control Register (PLLC)                             | 29 |

| 3.3.3   | · , , ,                                                 |    |

| 3.3.4   |                                                         |    |

| 3.3.5   | , ,                                                     |    |

| 3.3.6   |                                                         |    |

| 3.4     | Clock Modes                                             |    |

| 3.5     | Operations in Low Power Consumption Mode (Standby Mode) | 41 |

| 3.5.1   |                                                         |    |

| 3.5.2   | ,                                                       |    |

| 3.5.3   | ·                                                       |    |

| 3.5.4   | •                                                       |    |

| 3.5.5   |                                                         |    |

| 3.6     | Clock Oscillator Circuit                                |    |

| 3.7     | Overview of Prescaler                                   |    |

| 3.8     | Configuration of Prescaler                              |    |

| 3.9     | Operation of Prescaler                                  |    |

| 3.10    | Notes on Using Prescaler                                |    |

| CLIADTI | ED 4 DECET                                              | 64 |

| CHAPTI  | -                                                       |    |

| 4.1     | Reset Operation                                         |    |

| 4.2     | Register                                                |    |

| 4.2.1   |                                                         |    |

| 4.3     | Notes on Using Reset                                    | 70 |

| CHAPTI  | ER 5 INTERRUPTS                                         | 71 |

| 5.1     | Interrupts                                              | 72 |

| 5.1.1   | Interrupt Level Setting Registers (ILR0 to ILR5)        | 73 |

| 512     | Interrunt Processing                                    | 75 |

| 5.1.3  | Nested Interrupts                           | 77  |

|--------|---------------------------------------------|-----|

| 5.1.4  | Interrupt Processing Time                   | 78  |

| 5.1.5  | Stack Operation During Interrupt Processing | 79  |

| 5.1.6  | S Interrupt Processing Stack Area           | 80  |

| CHAPT  | ER 6                                        | 21  |

| 6.1    | Overview                                    |     |

| 6.2    | Configuration and Operations                |     |

| 0.2    | Configuration and Operations                |     |

| CHAPT  | _                                           |     |

| 7.1    | Overview                                    |     |

| 7.2    | Configuration                               |     |

| 7.3    | Interrupt                                   |     |

| 7.4    | Operations and Setting Procedure Example    | 92  |

| 7.5    | Register                                    |     |

| 7.5.1  | <b>5</b> ( ,                                |     |

| 7.6    | Notes on Using Time-base Timer              | 98  |

| CHAPTI | ER 8 HARDWARE/SOFTWARE WATCHDOG TIMER       | 99  |

| 8.1    | Overview                                    |     |

| 8.2    | Configuration                               |     |

| 8.3    | Operations and Setting Procedure Example    |     |

| 8.4    | Register                                    |     |

| 8.4.1  | <u> </u>                                    |     |

| 8.5    | Notes on Using Watchdog Timer               |     |

|        |                                             |     |

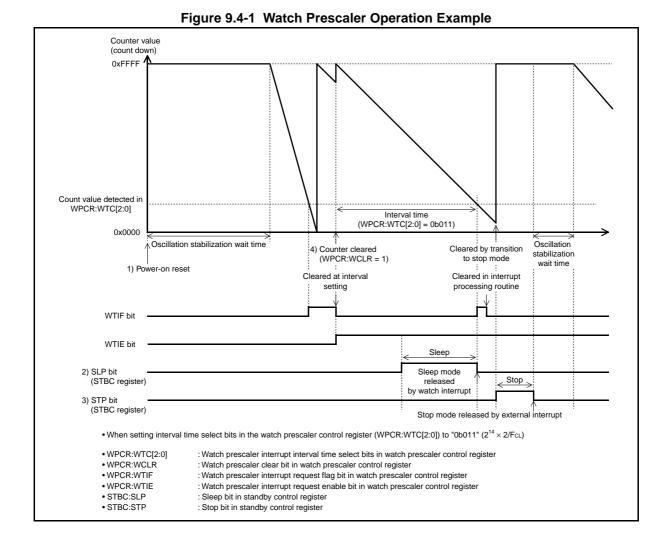

| CHAPT  | ER 9 WATCH PRESCALER                        | 111 |

| 9.1    | Overview                                    | 112 |

| 9.2    | Configuration                               | 113 |

| 9.3    | Interrupt                                   | 115 |

| 9.4    | Operations and Setting Procedure Example    | 116 |

| 9.5    | Register                                    | 119 |

| 9.5.1  | Watch Prescaler Control Register (WPCR)     | 120 |

| 9.6    | Notes on Using Watch Prescaler              | 122 |

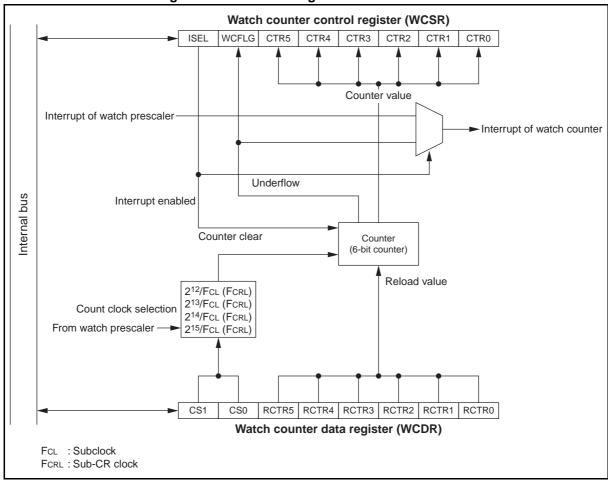

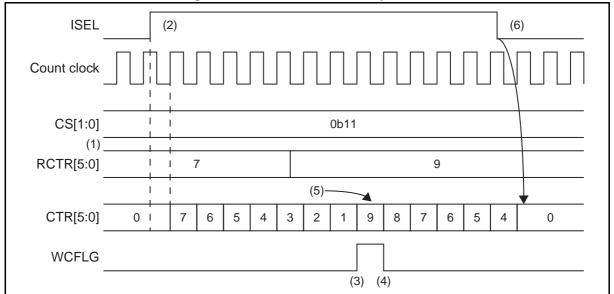

| СНАРТІ | ER 10 WATCH COUNTER                         | 123 |

| 10.1   | Overview                                    |     |

| 10.1   | Configuration                               |     |

|        | · ·                                         |     |

| 10.3   | Interrupt                                   |     |

| 10.4   | Operations and Setting Procedure Example    |     |

| 10.5   | Registers                                   |     |

| 10.5.  | <b>5</b>                                    |     |

| 10.5.  | <b>5</b> ( )                                |     |

| 10.6   | Notes on Using Watch Counter                | 133 |

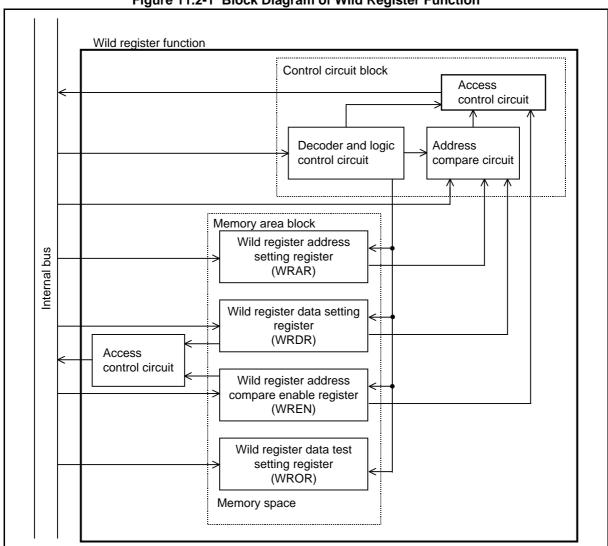

| CHAPT  | ER 11 WILD REGISTER FUNCTION                | 135 |

| 11.1   | Overview                                    | 136 |

| 11.2   | Configuration                               |     |

|        | Operations                                  |     |

| 11  | .4    | Registers                                                             | 140 |

|-----|-------|-----------------------------------------------------------------------|-----|

| 1   | 1.4.1 | Wild Register Data Setting Registers (WRDR0 to WRDR2)                 | 141 |

| 1   | 1.4.2 | Wild Register Address Setting Registers (WRAR0 to WRAR2)              | 142 |

| 1   | 1.4.3 | Wild Register Address Compare Enable Register (WREN)                  | 143 |

| 1   | 1.4.4 | Wild Register Data Test Setting Register (WROR)                       | 144 |

| 11  | .5    | Typical Hardware Connection Example                                   | 145 |

| СНА | PTE   | R 12 8/16-BIT COMPOSITE TIMER                                         | 147 |

| 12  | .1    | Overview                                                              | 148 |

| 12  | .2    | Configuration                                                         | 150 |

| 12  | .3    | Channel                                                               | 153 |

| 12  | .4    | Pins                                                                  | 154 |

| 12  | .5    | Interrupts                                                            | 155 |

| 12  | .6    | Operation of Interval Timer Function (One-shot Mode)                  | 156 |

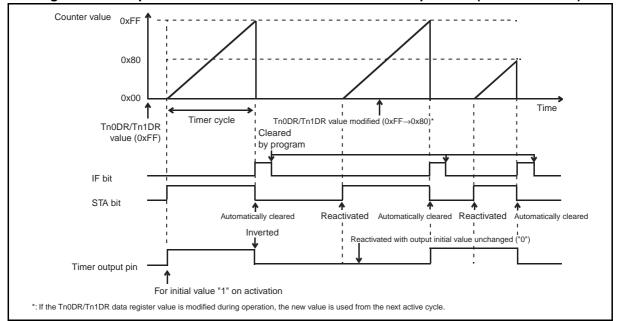

| 12  | .7    | Operation of Interval Timer Function (Continuous Mode)                | 158 |

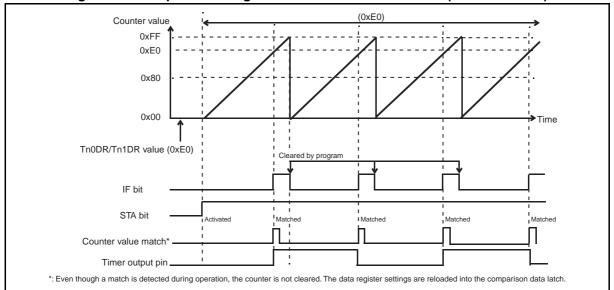

| 12  |       | Operation of Interval Timer Function (Free-run Mode)                  |     |

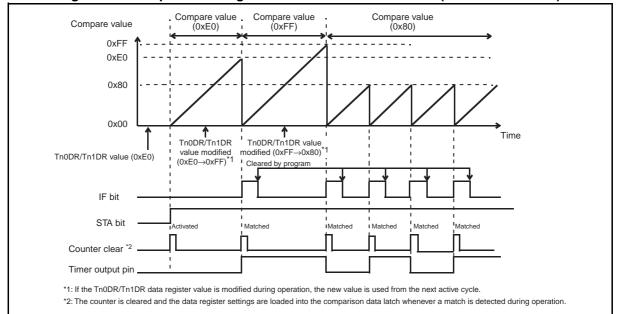

| 12  |       | Operation of PWM Timer Function (Fixed-cycle mode)                    |     |

| 12  | .10   | Operation of PWM Timer Function (Variable-cycle Mode)                 | 164 |

| 12  | .11   | Operation of PWC Timer Function                                       | 166 |

| 12  |       | Operation of Input Capture Function                                   |     |

|     |       | Operation of Noise Filter                                             |     |

|     |       | Registers                                                             |     |

|     |       | .1 8/16-bit Composite Timer Status Control Register 0 (Tn0CR0/Tn1CR0) |     |

|     |       | .2 8/16-bit Composite Timer Status Control Register 1 (Tn0CR1/Tn1CR1) |     |

|     |       | .3 8/16-bit Composite Timer Timer Mode Control Register (TMCRn)       |     |

|     |       | 4 8/16-bit Composite Timer Data Register (Tn0DR/Tn1DR)                |     |

| 12  | .15   | Notes on Using 8/16-bit Composite Timer                               | 185 |

| СНА | PTE   | R 13 EXTERNAL INTERRUPT CIRCUIT                                       | 187 |

| 13  | .1    | Overview                                                              | 188 |

| 13  |       | Configuration                                                         |     |

| 13  | .3    | Channels                                                              | 190 |

| 13  |       | Pin                                                                   |     |

| 13  |       | Interrupt                                                             |     |

| 13  |       | Operations and Setting Procedure Example                              | 193 |

| 13  | .7    | Register                                                              |     |

|     | 3.7.1 |                                                                       |     |

| 13  | .8    | Notes on Using External Interrupt Circuit                             | 198 |

| СНА | PTE   | R 14 INTERRUPT PIN SELECTION CIRCUIT                                  | 199 |

| 14  | .1    | Overview                                                              | 200 |

| 14  | .2    | Configuration                                                         | 201 |

| 14  | .3    | Pins                                                                  | 202 |

| 14  | .4    | Operation                                                             | 203 |

| 14  | .5    | Register                                                              | 204 |

| 1   | 4.5.1 | Interrupt Pin Selection Circuit Control Register (WICR)               | 205 |

| 14  | .6    | Notes on Using Interrupt Pin Selection Circuit                        | 208 |

| CHAPT | ER 15 LIN-UART                                                    | . 209 |

|-------|-------------------------------------------------------------------|-------|

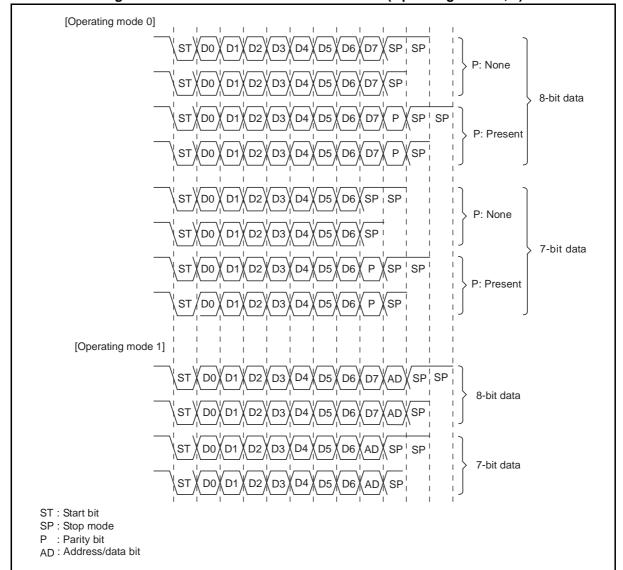

| 15.1  | Overview                                                          | 210   |

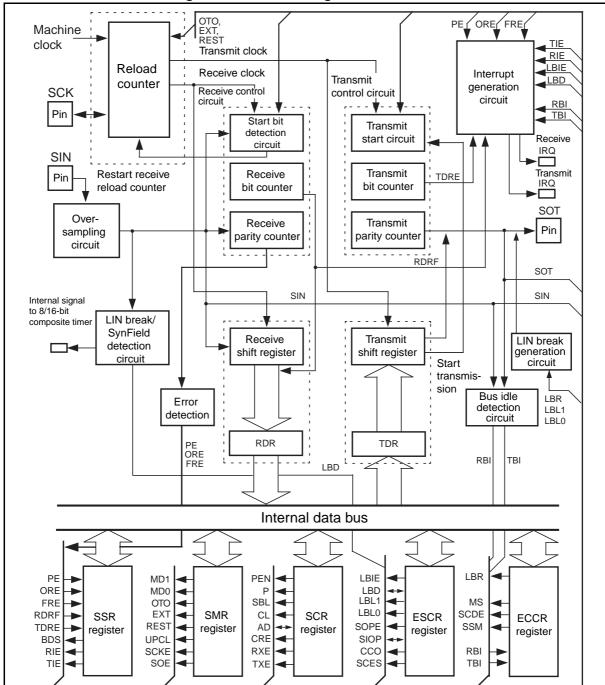

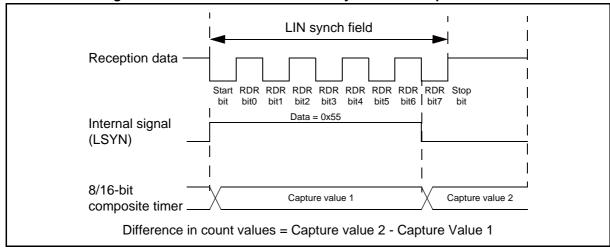

| 15.2  | Configuration                                                     | 212   |

| 15.3  | Pins                                                              | 217   |

| 15.4  | Interrupts                                                        | 218   |

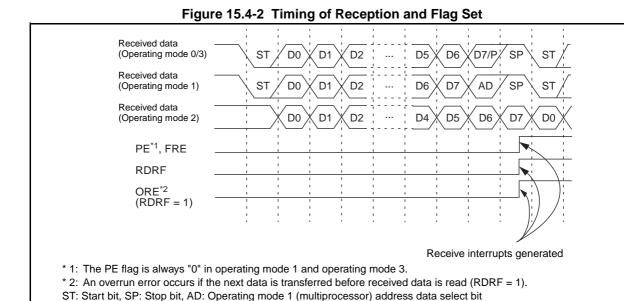

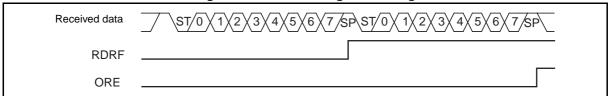

| 15.4  | .1 Timing of Receive Interrupt Generation and Flag Set            | . 221 |

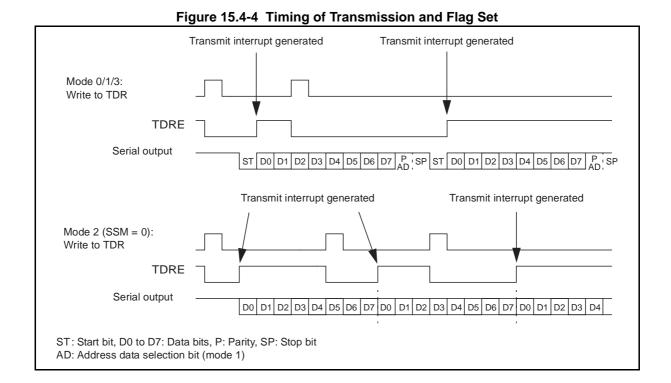

| 15.4  | .2 Timing of Transmit Interrupt Generation and Flag Set           | 223   |

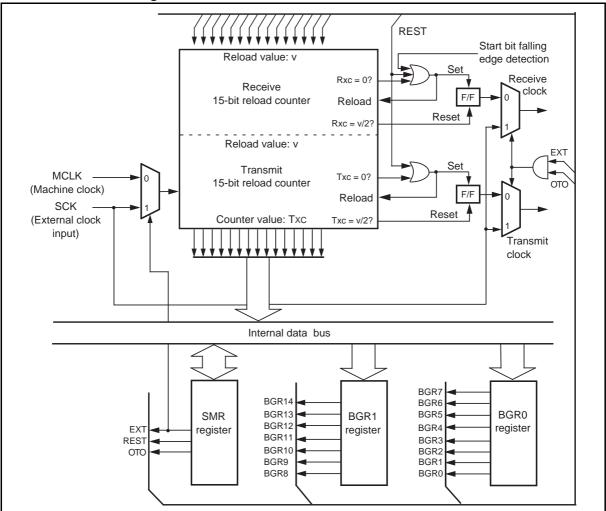

| 15.5  | LIN-UART Baud Rate                                                | 225   |

| 15.5  | .1 Baud Rate Setting                                              | 227   |

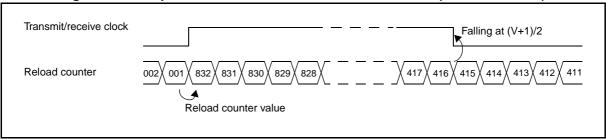

| 15.5  | .2 Reload Counter                                                 | . 231 |

| 15.6  | Operations and Setting Procedure Example                          |       |

| 15.6  |                                                                   |       |

| 15.6  | , , ,                                                             |       |

| 15.6  | , ,                                                               |       |

| 15.6  |                                                                   |       |

| 15.6  | ,                                                                 |       |

| 15.6  | ,                                                                 |       |

| 15.6  |                                                                   |       |

| 15.6  | ` ' ' ' ' '                                                       |       |

| 15.7  | Registers                                                         |       |

| 15.7  | 3 ( )                                                             |       |

| 15.7  |                                                                   |       |

| 15.7  | <b>3</b>                                                          |       |

| 15.7  |                                                                   |       |

| 15.7  |                                                                   |       |

| 15.7  | • , ,                                                             |       |

| 15.7  |                                                                   |       |

| 15.8  | Notes on Using LIN-UART                                           | 270   |

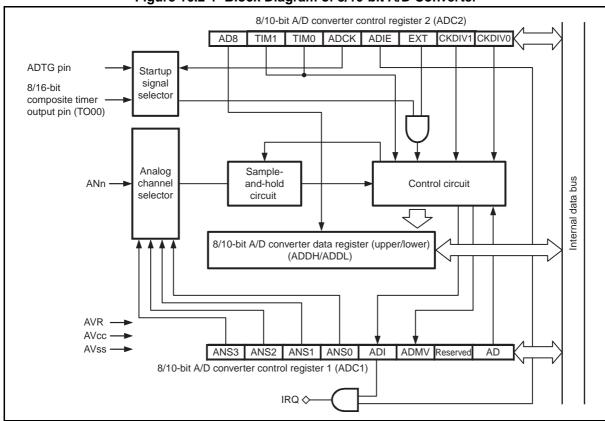

| CHAPT | ER 16 8/10-BIT A/D CONVERTER                                      | 275   |

| 16.1  | Overview                                                          | 276   |

| 16.2  | Configuration                                                     | 277   |

| 16.3  | Pins                                                              | 279   |

| 16.4  | Interrupt                                                         | 280   |

| 16.5  | Operations and Setting Procedure Example                          | 281   |

| 16.6  | Registers                                                         | 284   |

| 16.6  | .1 8/10-bit A/D Converter Control Register 1 (ADC1)               | 285   |

| 16.6  | .2 8/10-bit A/D Converter Control Register 2 (ADC2)               | 287   |

| 16.6  | .3 8/10-bit A/D Converter Data Register (Upper/Lower) (ADDH/ADDL) | 289   |

| 16.7  | Notes on Using 8/10-bit A/D Converter                             | . 290 |

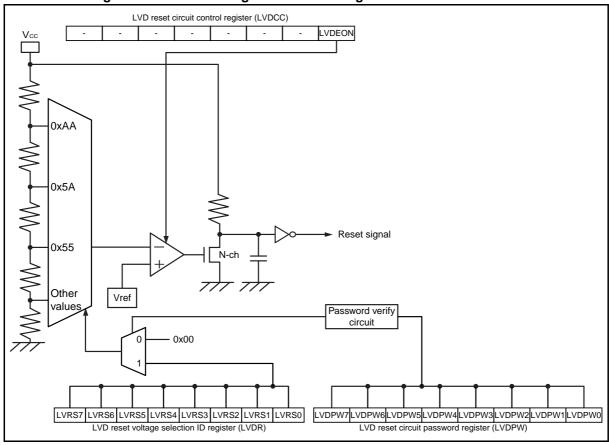

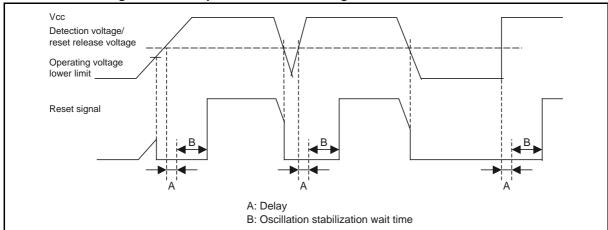

| CHAPT | ER 17 LOW-VOLTAGE DETECTION RESET CIRCUIT                         | 293   |

| 17.1  | Overview                                                          |       |

| 17.2  | Configuration                                                     |       |

| 17.3  | Pins                                                              |       |

| 17.4  | Operation                                                         |       |

| 17.5  | Registers                                                         |       |

| 17.5  | •                                                                 |       |

|       | .2 LVD Reset Circuit Password Register (LVDPW)                    |       |

| 17.5  | .3 LVD Reset Circuit Control Register (LVDCC)                    | 301   |

|-------|------------------------------------------------------------------|-------|

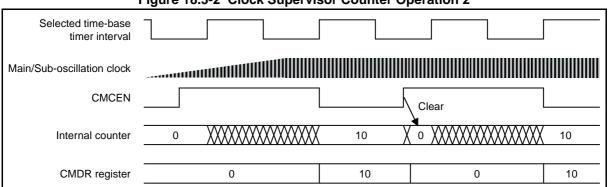

| CHAPT | ER 18 CLOCK SUPERVISOR COUNTER                                   | . 303 |

| 18.1  | Overview                                                         | 304   |

| 18.2  | Configuration                                                    | 305   |

| 18.3  | Operations                                                       |       |

| 18.4  | Registers                                                        |       |

| 18.4  |                                                                  |       |

| 18.4  |                                                                  |       |

| 18.5  | Notes on Using Clock Supervisor Counter                          |       |

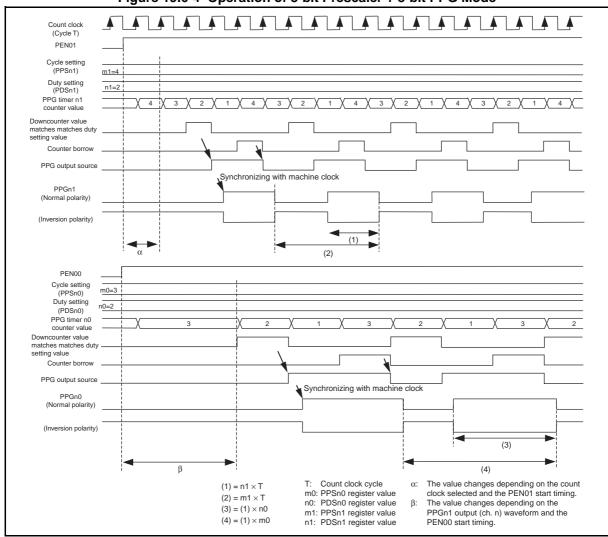

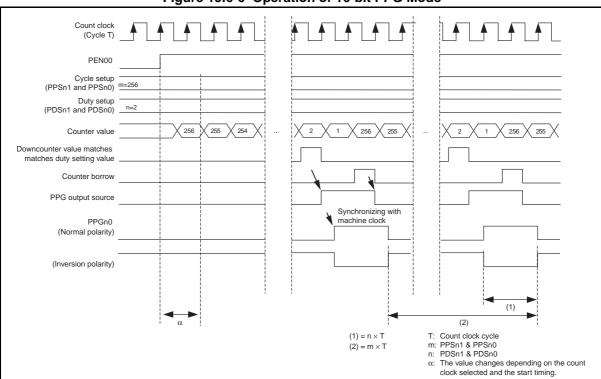

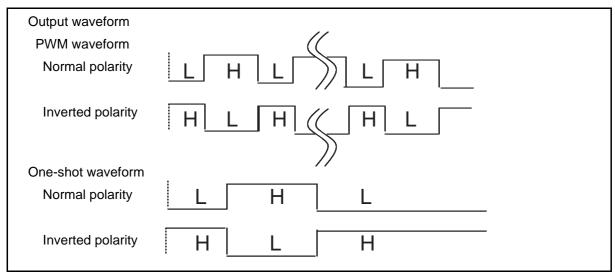

| CHAPT | ER 19 8/16-BIT PPG                                               | . 319 |

| 19.1  | Overview                                                         | 320   |

| 19.2  | Configuration                                                    |       |

| 19.3  | Channel                                                          |       |

| 19.4  | Pins                                                             |       |

| 19.5  | Interrupt                                                        |       |

| 19.6  | Operations and Setting Procedure Example                         |       |

| 19.6  | ·                                                                |       |

| 19.6  | ·                                                                |       |

|       |                                                                  |       |

| 19.6  |                                                                  |       |

| 19.7  | Registers                                                        |       |

| 19.7  | <b>5</b> ( )                                                     |       |

| 19.7  | <b>0</b> ( ,                                                     |       |

| 19.7  | , , ,                                                            |       |

| 19.7  | , , ,                                                            |       |

| 19.7  | 9 ( )                                                            |       |

| 19.7  | 1 ,                                                              |       |

| 19.8  | Notes on Using 8/16-bit PPG                                      | 345   |

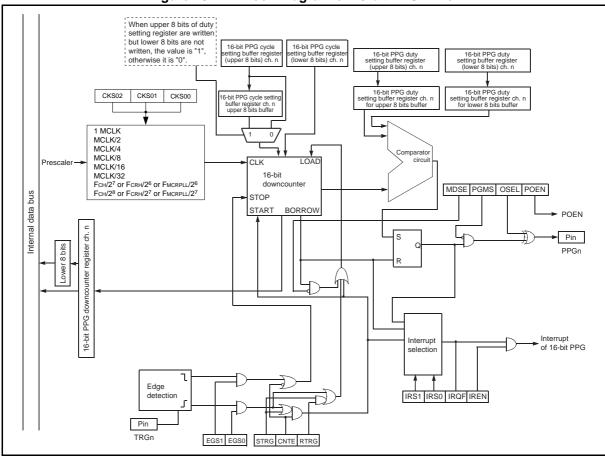

| CHAPT | ER 20 16-BIT PPG TIMER                                           | . 347 |

| 20.1  | Overview                                                         | 348   |

| 20.2  | Configuration                                                    | 349   |

| 20.3  | Channel                                                          | 351   |

| 20.4  | Pins                                                             | 352   |

| 20.5  | Interrupts                                                       | 353   |

| 20.6  | Operations and Setting Procedure Example                         |       |

| 20.7  | Registers                                                        |       |

| 20.7  | <u> </u>                                                         |       |

| 20.7  | .2 16-bit PPG Cycle Setting Buffer Register (Upper/ Lower) ch. n |       |

| 00 -  | (PCSRHn/PCSRLn)                                                  |       |

| 20.7  | , , , , , , , , , , , , , , , , , , , ,                          |       |

| 20.7  |                                                                  |       |

| 20.7  |                                                                  |       |

| 20.8  | Notes on Using 16-bit PPG Timer                                  | 366   |

| CHAPT | ER 21 16-BIT RELOAD TIMER                                        | . 367 |

| 21.1  | Overview                                                         | 368   |

| 21.2  | Configuration                                                    | 370   |

|   | 21.3          | Channel                                                                          | . 372 |

|---|---------------|----------------------------------------------------------------------------------|-------|

|   | 21.4          | Pins                                                                             | . 373 |

|   | 21.5          | Interrupt                                                                        | . 374 |

|   | 21.6          | Operations and Setting Procedure Example                                         | . 375 |

|   | 21.6.         | 1 Internal Clock Mode                                                            | . 377 |

|   | 21.6.2        | 2 Event Count Mode                                                               | . 381 |

|   | 21.7          | Registers                                                                        | . 383 |

|   | 21.7.         | 1 16-bit Reload Timer Control Status Register (Upper) ch. n (TMCSRHn)            | . 384 |

|   | 21.7.2        | 2 16-bit Reload Timer Control Status Register (Lower) ch. n (TMCSRLn)            | . 386 |

|   | 21.7.3        | 3 16-bit Reload Timer Timer Register (Upper/Lower) ch. n (TMRHn/TMRLn)           | . 388 |

|   | 21.7.4        | 16-bit Reload Timer Reload Register (Upper/Lower) ch. n (TMRLRHn/TMRLRLn)        | . 389 |

|   | 21.8          | Notes on Using 16-bit Reload Timer                                               | . 390 |

| С | HAPTE         | ER 22 UART/SIO                                                                   | 391   |

| _ | 22.1          | Overview                                                                         |       |

|   | 22.2          | Configuration                                                                    |       |

|   | 22.3          | Channel                                                                          |       |

|   | 22.4          | Pins                                                                             |       |

|   | 22.5          | Interrupts                                                                       |       |

|   | 22.6          | Operations and Setting Procedure Example                                         |       |

|   | 22.6.         | •                                                                                |       |

|   | 22.6.2        | ·                                                                                |       |

|   | 22.7          | Registers                                                                        |       |

|   | 22.7.         |                                                                                  |       |

|   | 22.7.2        | · , ,                                                                            |       |

|   | 22.7.3        | , ,                                                                              |       |

|   | 22.7.4        | - , , , , , , , , , , , , , , , , , , ,                                          |       |

|   | 22.7.         | · · · · · · · · · · · · · · · · · · ·                                            |       |

| C | НДРТЕ         | ER 23 UART/SIO DEDICATED BAUD RATE GENERATOR                                     | 421   |

| _ | 23.1          | Overview                                                                         |       |

|   | 23.2          | Channel                                                                          |       |

|   | 23.3          | Operations                                                                       |       |

|   | 23.4          | Registers                                                                        |       |

|   | 23.4.         | UART/SIO Dedicated Baud Rate Generator Prescaler Select Register ch. n           |       |

|   | 23.4.2        | (PSSRn)2 UART/SIO Dedicated Baud Rate Generator Baud Rate Setting Register ch. n | . 420 |

|   | 23.4.2        | (BRSRn)                                                                          | . 427 |

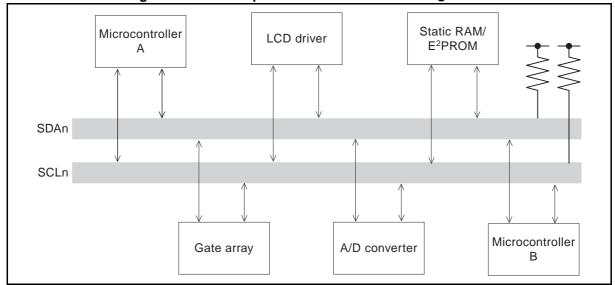

| C | НДРТЕ         | ER 24 I <sup>2</sup> C BUS INTERFACE                                             | 429   |

| J | 24.1          | Overview                                                                         |       |

|   | 24.2          | Configuration                                                                    |       |

|   | 24.2          | Channel                                                                          |       |

|   | 24.3          | Pins                                                                             |       |

|   | 24.4          | Interrupts                                                                       |       |

|   | 24.5          | Operations and Setting Procedure Example                                         |       |

|   | 24.6<br>24.6. |                                                                                  |       |

|   | 24.6.2        |                                                                                  |       |

|   | _             | Registers                                                                        |       |

|   |               |                                                                                  |       |

| 24.7.            | I I <sup>2</sup> C Bus Control Register 0 ch. n (IBCR0n) | 450 |

|------------------|----------------------------------------------------------|-----|

| 24.7.2           | 2 I <sup>2</sup> C Bus Control Register 1 ch. n (IBCR1n) | 453 |

| 24.7.3           | B I <sup>2</sup> C Bus Status Register ch. n (IBSRn)     | 457 |

| 24.7.4           | I <sup>2</sup> C Data Register ch. n (IDDRn)             | 460 |

| 24.7.            | 5 I <sup>2</sup> C Address Register ch. n (IAARn)        | 461 |

| 24.7.6           |                                                          |     |

| 24.8             | Notes on Using I <sup>2</sup> C Bus Interface            |     |

|                  |                                                          |     |

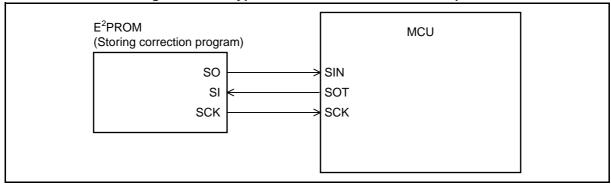

| CHAPTE           | R 25 EXAMPLE OF SERIAL PROGRAMMING CONNECTION            | 467 |

| 25.1             | Basic Configuration of Serial Programming Connection     | 468 |

| 25.2             | Example of Serial Programming Connection                 |     |

|                  |                                                          |     |

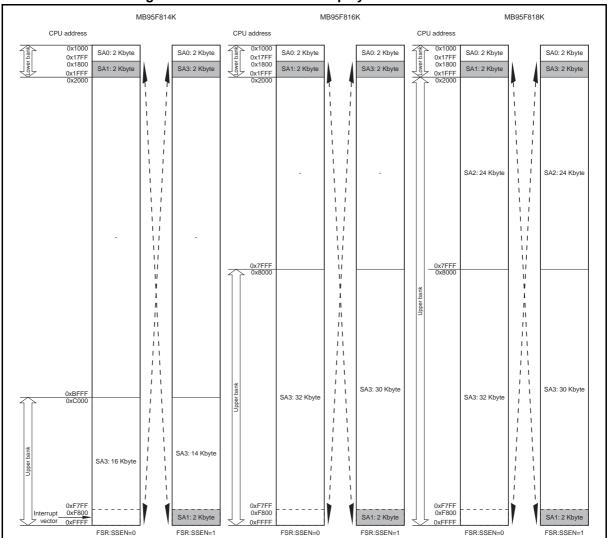

| CHAPTE           | R 26 DUAL OPERATION FLASH MEMORY                         | 471 |

| 26.1             | Overview                                                 |     |

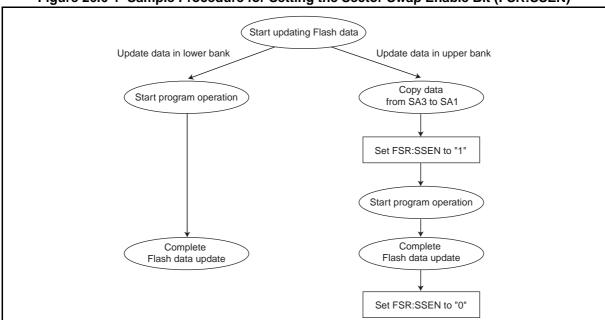

| 26.2             | Sector/Bank Configuration                                |     |

| 26.3             | Invoking Flash Memory Automatic Algorithm                |     |

| 26.4             | Checking Automatic Algorithm Execution Status            |     |

| 26.4.            |                                                          |     |

| 26.4.2           |                                                          |     |

| 26.4.3           |                                                          |     |

| 26.4.4           |                                                          |     |

| 26.4.5           |                                                          |     |

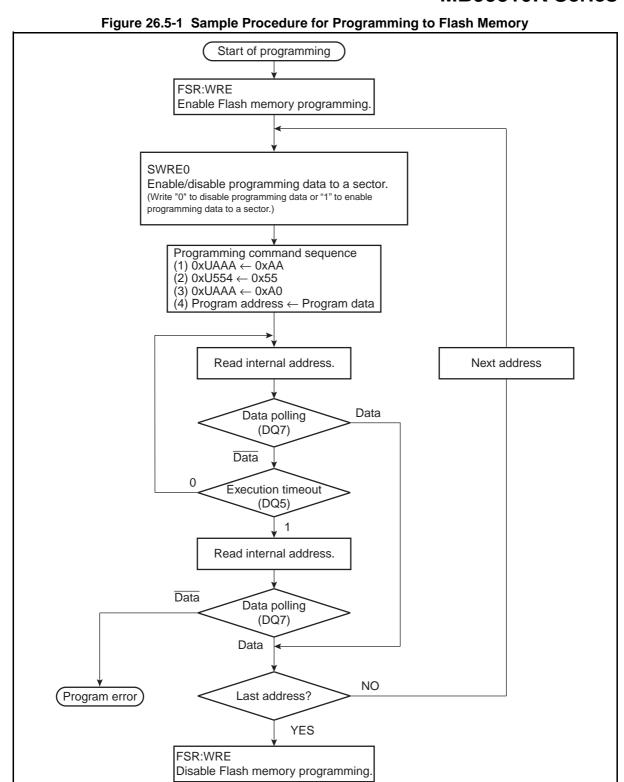

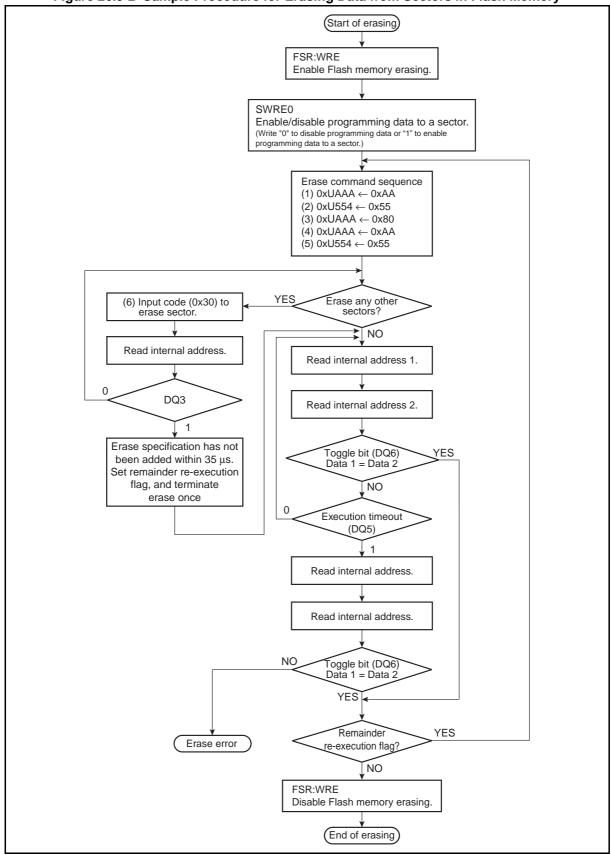

| 26.5             | Programming/Erasing Flash Memory                         |     |

| 26.5.            | · · · · · · · · · · · · · · · · · · ·                    |     |

| 26.5.2           |                                                          |     |

| 26.5.3           | ·                                                        |     |

| 26.5.4           |                                                          |     |

| 26.5.            | <b>3</b> 1                                               |     |

| 26.5.6           | ,                                                        |     |

| 26.5.7           | ,                                                        |     |

| 26.6             | Operations                                               |     |

|                  | Flash Security                                           |     |

| 26.8             | Registers                                                |     |

| 26.8.            | -                                                        |     |

|                  |                                                          |     |

| 26.8.2<br>26.8.3 | , , ,                                                    |     |

|                  |                                                          |     |

| 26.8.4           |                                                          |     |

| 26.8.5           | , , ,                                                    |     |

| 26.9             | Notes on Using Dual Operation Flash Memory               | 516 |

| CHADTE           | TR 27 NON VOLATILE DECISTED (NVD) INTERFACE              | E47 |

|                  | R 27 NON-VOLATILE REGISTER (NVR) INTERFACE               |     |

| 27.1             | Overview                                                 |     |

| 27.2             | Configuration                                            |     |

| 27.3             | Registers                                                |     |

| 27.3.            | 3 3 (11 / ( /                                            |     |

| 27.3.2           |                                                          |     |

| 27.3.3           | , , ,                                                    |     |

| 27.3.4           |                                                          |     |

| 27.4             | Notes on Main CR Clock Trimming                          | 525 |

| 27.5                                                        | Notes on Using NVR Interface                                                                                                                                            | 527               |

|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| CHAPT                                                       | TER 28 COMPARATOR                                                                                                                                                       | 529               |

| 28.1                                                        | Overview                                                                                                                                                                | 530               |

| 28.2                                                        | Configuration                                                                                                                                                           | 531               |

| 28.3                                                        | Dedicated BGR                                                                                                                                                           | 533               |

| 28.4                                                        | Pins                                                                                                                                                                    | 534               |

| 28.5                                                        | Interrupt                                                                                                                                                               | 535               |

| 28.6                                                        | Operations and Setting Procedure Example                                                                                                                                | 536               |

| 28.7                                                        | Register                                                                                                                                                                | 538               |

| 28.7                                                        | 7.1 Comparator Control Register ch. n (CMRn)                                                                                                                            | 539               |

|                                                             |                                                                                                                                                                         |                   |

| СНАРТ                                                       | TER 29 SYSTEM CONFIGURATION CONTROLLER                                                                                                                                  |                   |

| <b>CHAPT</b><br>29.1                                        | TER 29 SYSTEM CONFIGURATION CONTROLLER                                                                                                                                  | 544               |

| <b>CHAPT</b> 29.1 29.2                                      | TER 29 SYSTEM CONFIGURATION CONTROLLER                                                                                                                                  | 544<br>545        |

| <b>CHAPT</b> 29.1 29.2 29.2                                 | TER 29 SYSTEM CONFIGURATION CONTROLLER  Overview                                                                                                                        |                   |

| 29.1<br>29.2<br>29.2<br>29.2<br>APPEN                       | Overview                                                                                                                                                                | 544<br>545<br>546 |

| 29.1<br>29.2<br>29.2<br>29.2<br>APPEN                       | Overview                                                                                                                                                                |                   |

| 29.1<br>29.2<br>29.2<br>29.2<br>APPEN                       | Overview                                                                                                                                                                |                   |

| 29.1<br>29.2<br>29.2<br>29.2<br><b>APPEN</b><br>APPE<br>A.1 | TER 29 SYSTEM CONFIGURATION CONTROLLER                                                                                                                                  |                   |

| 29.1<br>29.2<br>29.2<br><b>APPEN</b><br>APPE<br>A.1<br>A.2  | Overview Register 2.1 System Configuration Register (SYSC)  IDIX ENDIX A Instruction Overview Addressing Special Instruction Bit Manipulation Instructions (SETB, CLRB) |                   |

# **Major revisions in this edition**

| Page | Revisions (For details, see their respective pages.) |

|------|------------------------------------------------------|

| _    | First edition                                        |

# CHAPTER 1

# MEMORY ACCESS MODE

This chapter describes the memory access mode.

1.1 Memory Access Mode

# 1.1 Memory Access Mode

The MB95810K Series supports only one memory access mode: single-chip mode.

# **■** Single-chip Mode

In single-chip mode, only the internal RAM and the Flash memory are used, and no external bus access is executed.

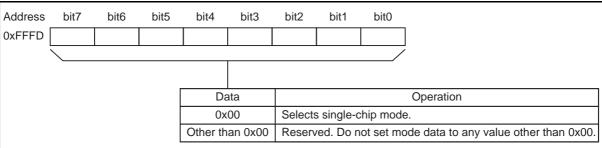

#### Mode data

Mode data is the data used to determine the memory access mode of the CPU.

The mode data address is fixed at "0xFFFD". Always set the mode data of the Flash memory to "0x00" to select the single-chip mode.

Figure 1.1-1 Mode Data Settings

After a reset is released, the CPU fetches mode data first.

The CPU then fetches the reset vector after the mode data. It starts executing instructions from the address set in the reset vector.

# **CHAPTER 2**

# *CPU*

This chapter describes the functions and operations of the CPU.

- 2.1 Dedicated Registers

- 2.2 General-purpose Register

- 2.3 Placement of 16-bit Data in Memory

# 2.1 Dedicated Registers

The CPU has dedicated registers: a program counter (PC), two registers for arithmetic operations (A and T), three address pointers (IX, EP, and SP), and the program status (PS) register. Each of the registers is 16 bits long. The PS register consists of the register bank pointer (RP), direct bank pointer (DP), and condition code register (CCR).

# ■ Configuration of Dedicated Registers

The dedicated registers in the CPU consist of seven 16-bit registers. As for the accumulator (A) and the temporary accumulator (T), using only the lower eight bits of the respective registers is also supported.

Figure 2.1-1 shows the configuration of the dedicated registers.

Initial value 16 bits 0xFFFD PC Program counter Indicates the address of the current instruction. 0x0000 AH ΑL : Accumulator (A) Temporary storage register for arithmetic operation and transfer 0x0000 TH Temporary accumulator (T) TL Performs arithmetic operations with the accumulator. 0x0000 IX Index register Indicates an index address. 0x0000 ΕP Extra pointer Indicates a memory address. 0x0000 SP Stack pointer Indicates the current stack location. 0x0030 RP DP **CCR** Program status Stores a register bank pointer, PS a direct bank pointer, and a condition code.

Figure 2.1-1 Configuration of Dedicated Registers

# **■** Functions of Dedicated Registers

#### Program counter (PC)

The program counter is a 16-bit counter which contains the memory address of the instruction currently executed by the CPU. The program counter is updated whenever an instruction is executed or an interrupt or a reset occurs. The initial value set immediately after a reset is the mode data read address (0xFFFD).

### Accumulator (A)

The accumulator is a 16-bit register for arithmetic operation. It is used for a variety of arithmetic and transfer operations of data in memory or data in other registers such as the temporary accumulator (T). The data in the accumulator can be handled either as word (16-bit) data or byte (8-bit) data. For byte-length arithmetic and transfer operations, only the lower eight bits (AL) of the accumulator are used with the upper eight bits (AH) left unchanged. The initial value set immediately after a reset is "0x0000".

#### Temporary accumulator (T)

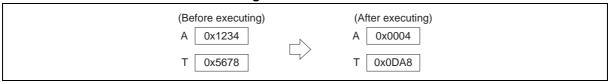

The temporary accumulator is an auxiliary 16-bit register for arithmetic operation. It is used to perform arithmetic operations with the data in the accumulator (A). The data in the temporary accumulator is handled as word data for word-length (16-bit) operations with the accumulator (A) and as byte data for byte-length (8-bit) operations. For byte-length operations, only the lower eight bits (TL) of the temporary accumulator are used and the upper eight bits (TH) are not used.

When a MOV instruction is used to transfer data to the accumulator (A), the previous contents of the accumulator are automatically transferred to the temporary accumulator. When transferring byte-length data, the upper eight bits (TH) of the temporary accumulator remain unchanged. The initial value after a reset is "0x0000".

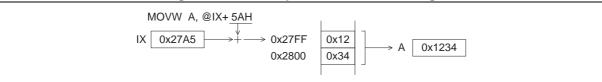

## Index register (IX)

The index register is a 16-bit register used to hold the index address. The index register is used with a single-byte offset (-128 to +127). The offset value is added to the index address to generate the memory address for data access. The initial value after a reset is "0x0000".

#### Extra pointer (EP)

The extra pointer is a 16-bit register which contains the value indicating the memory address for data access. The initial value after a reset is "0x0000".

#### Stack pointer (SP)

The stack pointer is a 16-bit register which holds the address referenced when an interrupt or a sub-routine call occurs and by the stack push and pop instructions. During program execution, the value of the stack pointer indicates the address of the most recent data pushed onto the stack. The initial value after a reset is "0x0000".

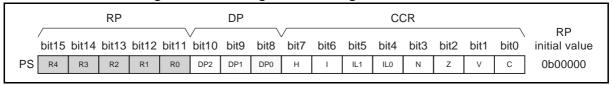

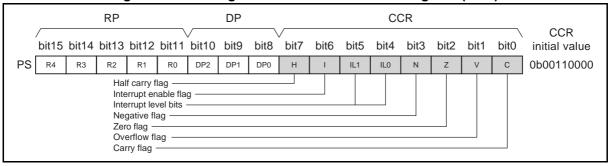

#### Program status (PS)

The program status is a 16-bit control register. The upper eight bits consists of the register bank pointer (RP) and direct bank pointer (DP); the lower eight bits consists of the condition code register (CCR).

In the upper eight bits, the upper five bits consists of the register bank pointer used to contain the address of the general-purpose register bank. The lower three bits consists of the direct bank pointer which locates the area to be accessed at high-speed by direct addressing.

The lower eight bits consists of the condition code register (CCR) which consists of flags that represent the state of the CPU.

The instructions that can access the program status are "MOVW A,PS" and "MOVW PS,A". The register bank pointer (RP) and direct bank pointer (DP) in the program status register can also be read from and written to by accessing the mirror address (0x0078).

Note that the condition code register (CCR) is a part of the program status register and cannot be accessed independently.

Refer to the "F<sup>2</sup>MC-8FX Programming Manual" for details on using the dedicated registers.

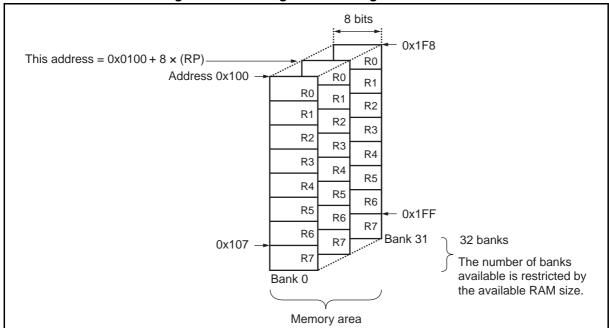

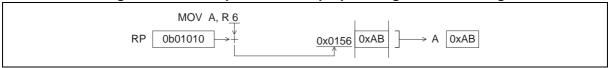

# 2.1.1 Register Bank Pointer (RP)

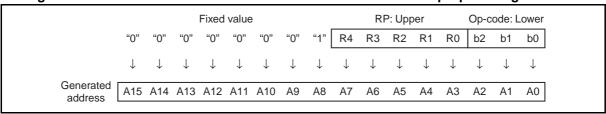

The register bank pointer (RP) in bit15 to bit11 of the program status (PS) register contains the address of the general-purpose register bank that is currently in use and is translated into a real address when general-purpose register addressing is used.

## ■ Configuration of Register Bank Pointer (RP)

Figure 2.1-2 shows the configuration of the register bank pointer.

Figure 2.1-2 Configuration of Register Bank Pointer

The register bank pointer contains the address of the register bank currently in use. The content of the register bank pointer is translated into a real address according to the rule shown in Figure 2.1-3.

Figure 2.1-3 Rule for Translation into Real Addresses in General-purpose Register Area

The register bank pointer specifies the register bank used as general-purpose registers in the RAM area. There are a total of 32 register banks, which are specified by setting a value between 0 and 31 in the upper five bits of the register bank pointer. Each register bank has eight 8-bit general-purpose registers which are selected by the lower three bits of the op-code.

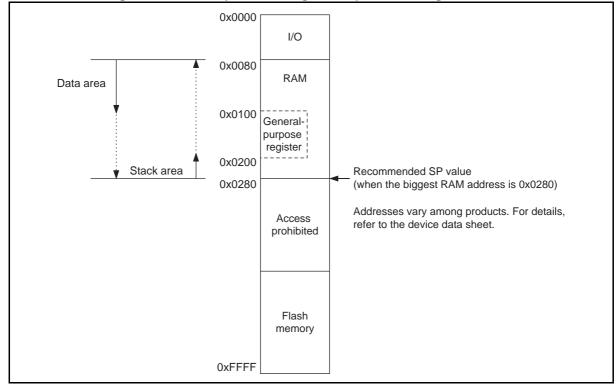

The register bank pointer allows the space from "0x0100" to "0x01FF"(max) to be used as a general-purpose register area. However, certain products have restrictions on the size of the area available for the general-purpose register area. The initial value of the register bank pointer after a reset is "0x0000".

#### ■ Mirror Address for Register Bank and Direct Bank Pointer

Values can be written to the register bank pointer (RP) and the direct bank pointer (DP) by accessing the program status (PS) register with the "MOVW PS,A" instruction; the two pointers can be read by accessing PS with the "MOVW A,PS" instruction. Values can also be directly written to and read from the two pointers by accessing "0x0078", the mirror address of the register bank pointer.

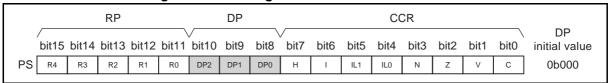

# 2.1.2 Direct Bank Pointer (DP)

The direct bank pointer (DP) in bit10 to bit8 of the program status (PS) register specifies the area to be accessed by direct addressing.

# ■ Configuration of Direct Bank Pointer (DP)

Figure 2.1-4 shows the configuration of the direct bank pointer.

Figure 2.1-4 Configuration of Direct Bank Pointer

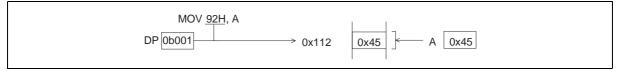

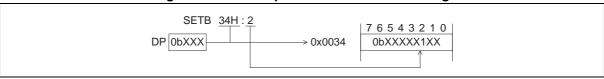

The area of "0x0000 to 0x007F" and that of "0x0090 to 0x047F" can be accessed by direct addressing. Access to 0x0000 to 0x007F is specified by an operand regardless of the value in the direct bank pointer. Access to 0x0090 to 0x047F is specified by the value of the direct bank pointer and the operand.

Table 2.1-1 shows the relationship between the direct bank pointer (DP) and the access area; Table 2.1-2 lists the direct addressing instructions.

Table 2.1-1 Direct Bank Pointer and Access Area

| Direct bank pointer (DP[2:0])       | Operand-specified dir | Access area*     |

|-------------------------------------|-----------------------|------------------|

| 0bXXX (It does not affect mapping.) | 0x0000 to 0x007F      | 0x0000 to 0x007F |

| 0b000 (Initial value)               | 0x0090 to 0x00FF      | 0x0090 to 0x00FF |

| 0b001                               |                       | 0x0100 to 0x017F |

| 0b010                               |                       | 0x0180 to 0x01FF |

| 0b011                               |                       | 0x0200 to 0x027F |

| 0b100                               | 0x0080 to 0x00FF      | 0x0280 to 0x02FF |

| 0b101                               |                       | 0x0300 to 0x037F |

| 0b110                               |                       | 0x0380 to 0x03FF |

| 0b111                               |                       | 0x0400 to 0x047F |

<sup>\*:</sup> The available access area varies among products. For details, refer to the device data sheet.

Table 2.1-2 Direct Address Instruction List

| Applicable instructions |  |  |  |

|-------------------------|--|--|--|

| CLRB dir:bit            |  |  |  |

| SETB dir:bit            |  |  |  |

| BBC dir:bit,rel         |  |  |  |

| BBS dir:bit,rel         |  |  |  |

| MOV A,dir               |  |  |  |

| CMP A,dir               |  |  |  |

| ADDC A,dir              |  |  |  |

| SUBC A,dir              |  |  |  |

| MOV dir,A               |  |  |  |

| XOR A,dir               |  |  |  |

| AND A,dir               |  |  |  |

| OR A,dir                |  |  |  |

| MOV dir,#imm            |  |  |  |

| CMP dir,#imm            |  |  |  |

| MOVW A,dir              |  |  |  |

| MOVW dir,A              |  |  |  |

# 2.1.3 Condition Code Register (CCR)

The condition code register (CCR) in the lower eight bits of the program status (PS) register consists of the bits (H, N, Z, V, and C) containing information about the arithmetic result or transfer data and the bits (I, IL1, and IL0) used to control the acceptance of interrupt requests.

## ■ Configuration of Condition Code Register (CCR)

Figure 2.1-5 Configuration of Condition Code Register (CCR)

The condition code register is a part of the program status (PS) register and therefore cannot be accessed independently.

# ■ Bits Showing Operation Results

## Half carry flag (H)

This flag is set to "1" when a carry from bit3 to bit4 or a borrow from bit4 to bit3 occurs due to the result of an operation. Otherwise, the flag is set to "0". Do not use this flag for any operation other than addition and subtraction as the flag is intended for decimal-adjusted instructions.

### Negative flag (N)

This flag is set to "1" when the value of the most significant bit is "1" due to the result of an operation, and is set to "0" when the value of the most significant bit is "0".

#### Zero flag (Z)

This flag is set to "1" when the result of an operation is "0", and is set to "0" when the result of an operation is a value other than "0".

#### Overflow flag (V)

This flag indicates whether the result of an operation has caused an overflow, with the operand used in the operation being regarded as an integer expressed as a complement of two. If an overflow occurs, the overflow flag is set to "1"; otherwise, it is set to "0".

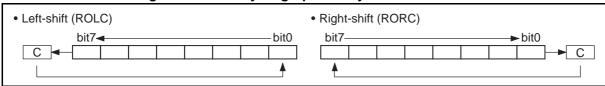

### Carry flag (C)

This flag is set to "1" when a carry from bit7 or a borrow to bit7 occurs due to the result of an operation. Otherwise, the flag is set to "0". When a shift instruction is executed, the flag is set to the shift-out value.

Figure 2.1-6 shows how the carry flag is updated by a shift instruction.

Figure 2.1-6 Carry Flag Updated by Shift Instruction

# ■ Interrupt Acceptance Control Bits

## Interrupt enable flag (I)

When this flag is set to "1", interrupts are enabled and accepted by the CPU. When this flag is set to "0", interrupts are disabled and rejected by the CPU.

The initial value after a reset is "0".

The SETI and CLRI instructions set and clear the flag to "1" and "0", respectively.

### Interrupt level bits (IL[1:0])

These bits indicate the level of the interrupt currently accepted by the CPU.

The interrupt level is compared with the value of the interrupt level setting register (ILR0 to ILR5) that corresponds to the interrupt request (IRQ00 to IRQ23) of each peripheral function.

The CPU services an interrupt request only when its interrupt level is smaller than the value of these bits with the interrupt enable flag set (CCR:I=1). Table 2.1-3 lists interrupt level priorities. The initial value after a reset is "0b11".

Table 2.1-3 Interrupt Levels

| IL1 | IL0 | Interrupt level | Priority           |

|-----|-----|-----------------|--------------------|

| 0   | 0   | 0               | High               |

| 0   | 1   | 1               | <b>A</b>           |

| 1   | 0   | 2               | ▼                  |

| 1   | 1   | 3               | Low (No interrupt) |

The interrupt level bits (IL[1:0]) are usually "0b11" when the CPU does not service an interrupt (with the main program running).

For details of interrupts, see "5.1 Interrupts".

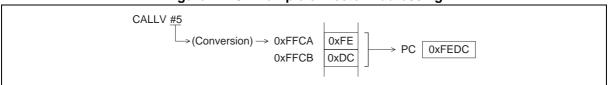

# 2.2 General-purpose Register

The general-purpose registers are a memory block in which each bank consists of eight 8-bit registers. Up to 32 register banks can be used in total. The register bank pointer (RP) is used to specify a register bank. Register banks are useful for interrupt handling, vector call processing, and sub-routine calls.

# ■ Configuration of General-purpose Register

- The general-purpose register is an 8-bit register and is located in a register bank in the general-purpose register area (in RAM).

- Up to 32 banks can be used, each of which consists of eight registers (R0 to R7).

- The register bank pointer (RP) specifies the register bank currently being used and the lower three bits of the op-code specify the general-purpose register 0 (R0) to the general-purpose register 7 (R7).

Figure 2.2-1 shows the configuration of the register banks.

Figure 2.2-1 Configuration of Register Banks

For information on the general-purpose register area available on each product, see "■ AREAS FOR SPECIFIC APPLICATIONS" in the device data sheet.

# **■** Features of General-purpose Registers

The general-purpose register has the following features.

- High-speed access to RAM with short instructions (general-purpose register addressing).

- Grouping registers into a block of register banks facilitates data protection and division of registers in terms of functions.

A general-purpose register bank can be allocated exclusively to an interrupt service routine or a vector call (CALLV #0 to #7) processing routine. For instance, the fourth register bank is always assigned to the second interrupt.

Data of a general-purpose register before an interrupt can be saved to a dedicated register bank by just specifying that register bank at the beginning of an interrupt service routine. This therefore eliminates the need to save data of a general-purpose register in a stack, thereby enabling the CPU to receive interrupts at high speed.

#### Note:

In an interrupt service routine, include one of the following in a program to ensure that values of the interrupt level bits (CCR:IL[1:0]) of the condition code register are not modified when modifying a register bank pointer (RP) to specify a register bank.

- Read the interrupt level bits and save their values before writing a value to the RP.

- Directly write a new value to the RP mirror address "0x0078" to update the RP.

- As for a product whose RAM size is 256 bytes, the area available for general-purpose

registers is from "0x0100" to "0x018F", which is half of that of the product whose RAM

size is 512 bytes or above. Therefore, when using a program development tool such

as a C compiler to set a general-purpose register area, ensure that the area used as a

general-purpose register area does not exceed the size of RAM installed.

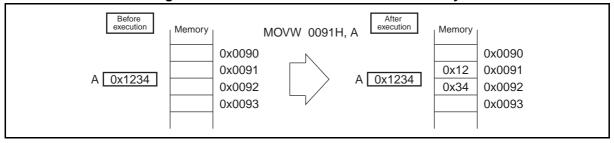

# 2.3 Placement of 16-bit Data in Memory

## This section describes how 16-bit data is stored in memory.

## ■ Placement of 16-bit Data in Memory

#### State of 16-bit data stored in RAM.

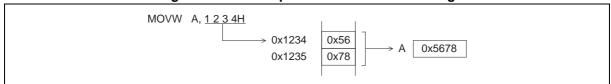

When 16-bit data is written to memory, the upper byte of the data is stored at a smaller address and the lower byte is stored at the next address. When 16-bit data is read, it is handled in the same way.

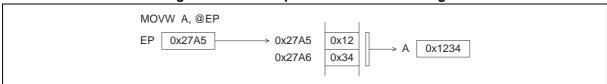

Figure 2.3-1 shows how 16-bit data is placed in memory.

Figure 2.3-1 Placement of 16-bit Data in Memory

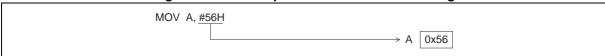

## Storage state of 16-bit data specified by an operand

Even when the operand in an instruction specifies 16-bit data, the upper byte is stored at the address closer to the op-code (instruction) and the lower byte is stored at the address next to the one at which the upper byte is stored.

That is true whether an operand is either a memory address or 16-bit immediate data.

Figure 2.3-2 shows how 16-bit data in an instruction is placed.

Figure 2.3-2 Placement of 16-bit Data in Instruction

```

[Example] MOV A, 5678H ; Extended address

MOVW A, #1234H; 16-bit immediate data

Assemble

OxXXX0 XX XX

OxXXX2 60 56 78 ; Extended address

OxXXX5 E4 12 34 ; 16-bit immediate data

OxXXX8 XX

:

```

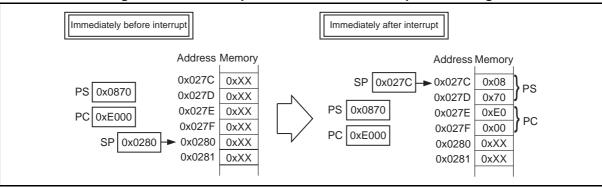

#### Storage state of 16-bit data in the stack

When 16-bit register data is saved in a stack on an interrupt, the upper byte is stored at a lower address in the same way as 16-bit data specified by an operand.

# CHAPTER 2 CPU 2.3 Placement of 16-bit Data in Memory

# MB95810K Series

14

# **CHAPTER 3**

# **CLOCK CONTROLLER**

# This chapter describes the functions and operations of the clock controller.

- 3.1 Overview

- 3.2 Oscillation Stabilization Wait Time

- 3.3 Registers

- 3.4 Clock Modes

- Operations in Low Power Consumption Mode (Standby Mode)

- 3.6 Clock Oscillator Circuit

- 3.7 Overview of Prescaler

- 3.8 Configuration of Prescaler

- 3.9 Operation of Prescaler

- 3.10 Notes on Using Prescaler

# 3.1 Overview

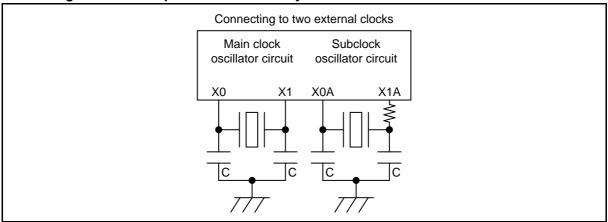

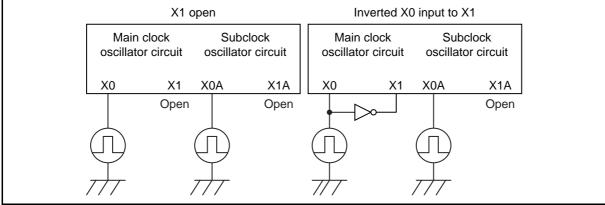

The New 8FX family has a built-in clock controller that optimizes its power consumption. It supports both of the external main clock and the external subclock.

The clock controller enables/disables clock oscillation, enables/disables the supply of clock signals to the internal circuit, selects the clock source, and controls the internal CR oscillator and frequency divider circuits.

#### ■ Overview of Clock Controller

The clock controller enables/disables clock oscillation, enables/disables clock supply to the internal circuit, selects the clock source, and controls the internal CR oscillator and frequency divider circuits

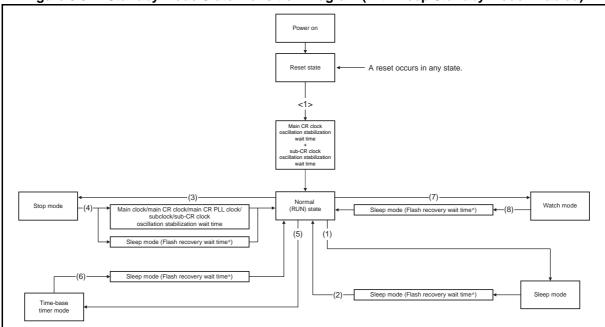

The clock controller controls the internal clock according to the clock mode, standby mode settings and the reset operation. The clock mode is used to select an internal operating clock; the standby mode is used to enable or disable clock oscillation and signal supply.

The clock controller selects the optimum power consumption and functions depending on the combination of clock mode and standby mode.

This device has five source clocks: a main clock formed by dividing the main oscillation clock by two, a subclock formed by dividing the sub-oscillation clock by two, a main CR clock, a main CR PLL clock formed by multiplying the main CR oscillation clock by the PLL multiplier, and a sub-CR clock formed by dividing the sub-CR oscillation clock by two.

# **■** Block Diagram of Clock Controller

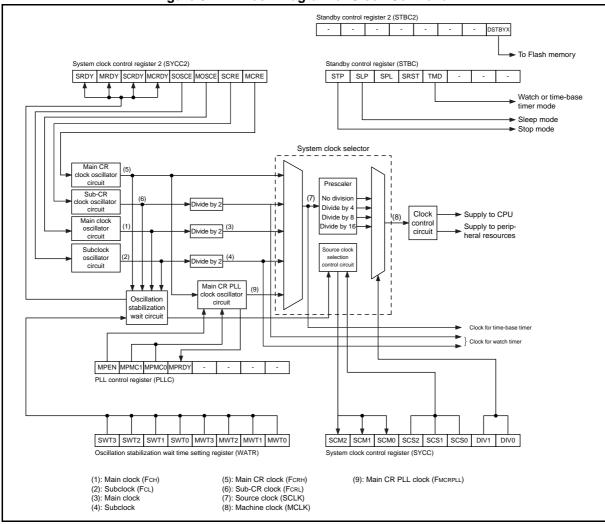

Figure 3.1-1 is the block diagram of the clock controller.

Figure 3.1-1 Block Diagram of Clock Controller

# **■** Configuration of Clock Controller

#### Main clock oscillator circuit

This block is the oscillator circuit for the main clock.

#### Subclock oscillator circuit

This block is the oscillator circuit for the subclock.

#### Main CR clock oscillator circuit

This block is the oscillator circuit for the main CR clock.

#### Main CR PLL clock oscillator circuit

This block is the oscillator circuit for the main CR PLL clock.

#### Sub-CR clock oscillator circuit

This block is the oscillator circuit for the sub-CR clock.

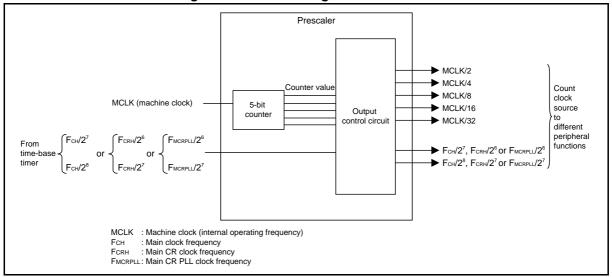

#### System clock selector

This block selects a clock according to the clock mode used from the following five types of source clock: main clock, subclock, main CR clock, main CR PLL clock and sub-CR clock. The source clock selected is divided by the prescaler. The divided clock is called "machine clock", which is to be supplied to the clock control circuit.

#### Clock control circuit

This block controls the supply of the machine clock to the CPU and each peripheral function according to the standby mode used or oscillation stabilization wait time.

#### Oscillation stabilization wait circuit

This block outputs oscillation stabilization wait time signals according to clocks that are enabled to operate.

In the case of main clock, its oscillation stabilization signal can be selected from 14 types of oscillation stabilization signals created by a dedicated timer in the oscillation stabilization wait circuit. In case of subclock, its oscillation stabilization signal can be selected from 15 types of oscillation stabilization signals created by the same dedicated timer.

#### System clock control register (SYCC)

This register selects a clock mode and a machine clock divide ratio, and indicates the current clock mode.

#### PLL control register (PLLC)

This register controls the main CR PLL clock multiplier settings.

#### Standby control register (STBC)

This register controls the transition from RUN state to standby mode, the setting of pin states in stop mode, time-base timer mode, or watch mode, and the generation of software resets.

• System clock control register 2 (SYCC2)

This register enables or disables the oscillations of the main clock, main CR clock, subclock, and sub-CR clock, and displays the ready signals of main clock oscillation, main CR clock oscillation, subclock oscillation and sub-CR clock oscillation.

Oscillation stabilization wait time setting register (WATR)

This register sets the oscillation stabilization wait times for the main clock and subclock.

• Standby control register 2 (STBC2)

This register controls the deep standby mode.

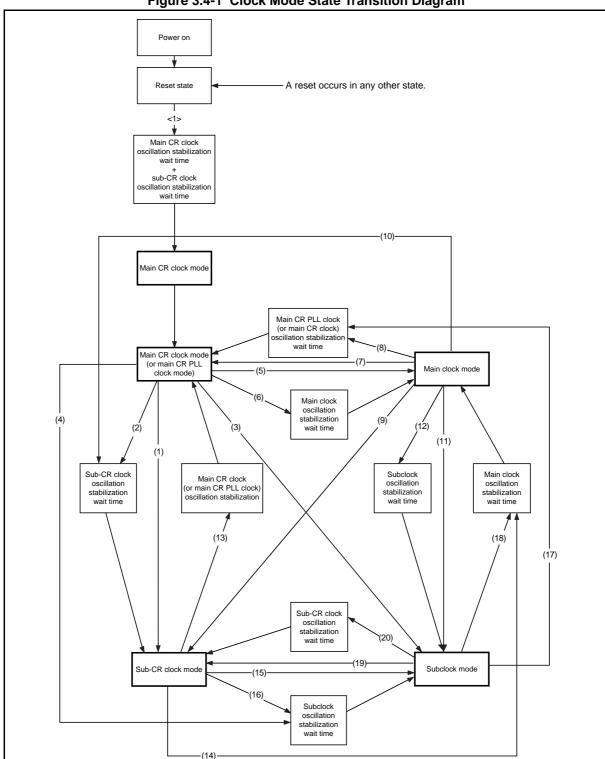

#### **■ Clock Modes**

There are five clock modes:

- Main clock mode

- Main CR clock mode

- Main CR PLL clock mode

- Subclock mode

- Sub-CR clock mode.

Table 3.1-1 shows the relationships between the clock modes and the machine clock (operating clock for the CPU and peripheral functions).

Table 3.1-1 Clock Modes and Machine Clock Selection

| Clock mode             | Machine clock                                                                        |

|------------------------|--------------------------------------------------------------------------------------|

| Main clock mode        | The machine clock is generated by dividing the main clock by two.                    |

| Main CR clock mode     | The machine clock is generated from the main CR clock.                               |

| Main CR PLL clock mode | The machine clock is generated by multiplying the main CR clock by a PLL multiplier. |

| Subclock mode          | The machine clock is generated by dividing the subclock by two.                      |

| Sub-CR clock mode      | The machine clock is generated by dividing the sub-CR clock by two.                  |

In any clock mode, the frequency of a selected clock can be divided.

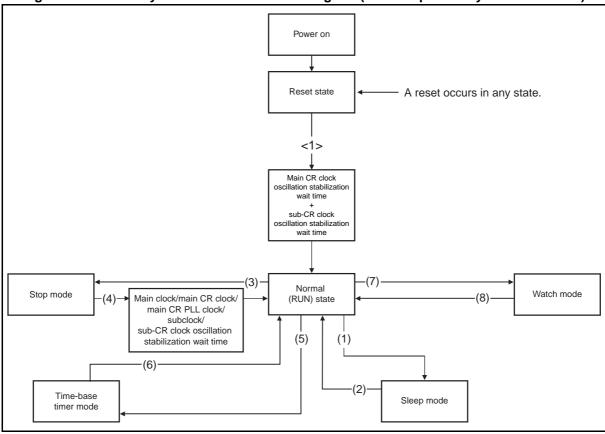

#### **■ Standby Mode**

The clock controller selects whether to enable or disable clock oscillation and clock supply to the internal circuitry according to the standby mode selected. With the exception of time-base timer mode and watch mode, the standby mode can be set independently of the clock mode.

Table 3.1-2 shows the relationships between standby modes and clock supply states.

Table 3.1-2 Standby Mode and Clock Supply States

| Standby mode         | Clock supply state                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sleep mode           | Clock supply to the CPU is stopped. As a result, the CPU stops operating, but other peripheral functions continue operating.                                                                                                                                                                                                                                                                            |

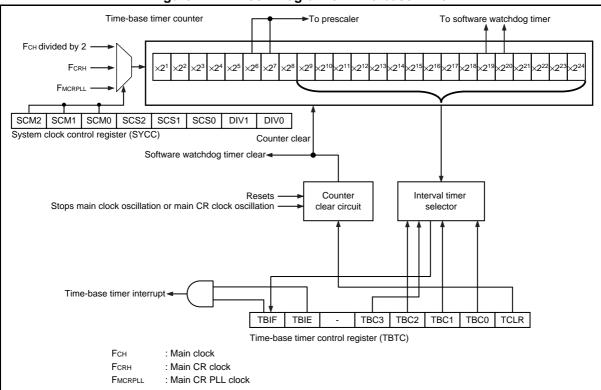

| Time-base timer mode | Clock signals are only supplied to the time-base timer and the watch prescaler, while the clock supply to other circuits is stopped. As a result, all the functions other than the time-base timer, watch prescaler, external interrupt, and low-voltage detection reset (option) are stopped.  The time-base timer mode can be used in main clock mode, main CR clock mode and main CR PLL clock mode. |

| Watch mode           | Main clock oscillation is stopped. Clock signals are supplied only to the watch prescaler, while clock supply to other circuits is stopped. As a result, all the functions other than the watch prescaler, external interrupt, and low-voltage detection reset (option) are stopped.  The watch mode is the standby mode that can be used in subclock mode and sub-CR clock mode.                       |

| Stop mode            | Main clock oscillation and subclock oscillation are stopped, and clock supply to all circuits is stopped. As a result, all the functions other than external interrupt and low-voltage detection reset (option) are stopped.                                                                                                                                                                            |

In every standby mode, two further operating mode options, normal standby mode and deep standby mode, can be selected by the deep standby mode control bit in the standby control register 2 (STBC2:DSTBYX).

For details, see "3.5.1 Notes on Using Standby Mode".

#### Note:

Clocks that are not mentioned in Table 3.1-2 are supplied under particular settings.

For example, with main clock mode being used in stop mode, when SYCC2:SOSCE or SYCC2:SCRE has been set to "1", the watch prescaler continues its operation.

In addition, with the hardware watchdog timer already started, the watchdog timer operates also in standby mode, depending on the settings of the non-volatile register (NVR) interface. For details of the non-volatile register (NVR) interface, see "CHAPTER 27 NON-VOLATILE REGISTER (NVR) INTERFACE".

#### **■** Combinations of Clock Mode and Standby Mode

Table 3.1-3 and Table 3.1-4 list the combinations of clock mode and standby mode, and the respective operating states of different internal circuits with different combinations of clock mode and standby mode.

Table 3.1-3 Combinations of Standby Mode and Clock Mode, and Internal Operating States (1)

|                                        |                    | RL                                                  | N                |                      | Sleep              |                                                     |                  |                      |

|----------------------------------------|--------------------|-----------------------------------------------------|------------------|----------------------|--------------------|-----------------------------------------------------|------------------|----------------------|

| Function                               | Main clock<br>mode | Main CR<br>clock mode/<br>Main CR PLL<br>clock mode | Subclock<br>mode | Sub-CR<br>clock mode | Main clock<br>mode | Main CR<br>clock mode/<br>Main CR PLL<br>clock mode | Subclock<br>mode | Sub-CR<br>clock mode |

| Main clock                             | Operating          | Stopped*1                                           | Stop             | pped                 | Operating          | Stopped*1                                           | Stop             | pped                 |

| Main CR clock/<br>Main CR PLL<br>clock | Stopped*2          | Operating                                           | Stop             | pped                 | Stopped*2          | Operating                                           | Stop             | pped                 |

| Subclock                               | Opera              | ating*3                                             | Operating        | Operating*3          | Opera              | nting*3                                             | Operating        | Operating*3          |

| Sub-CR clock                           | Operating*4        |                                                     | Operating*4      | Operating            | Opera              | nting*4                                             | Operating*4      | Operating            |

| CPU                                    | Operating          |                                                     | Operating        |                      | Stopped            |                                                     | Stopped          |                      |

| Flash memory                           | Operating          |                                                     | Operating        |                      | Value held*6       |                                                     | Value held*6     |                      |

| RAM                                    | Operating          |                                                     | Operating        |                      | Value              | e held                                              | Value            | e held               |

| I/O ports                              | Operating          |                                                     | Operating        |                      | Outpu              | ıt held                                             | Outpu            | ıt held              |

| Time-base timer                        | Ope                | rating                                              | Stopped          |                      | Oper               | rating                                              | Stop             | pped                 |

| Watch prescaler                        | Operat             | ing*3, *4                                           | Operating        |                      | Operating*3, *4    |                                                     | Operating        |                      |

| External interrupt                     | Operating          |                                                     | Operating        |                      | Operating          |                                                     | Operating        |                      |

| Hardware<br>watchdog timer             | Operating          |                                                     | Operating        |                      | Operating*5        |                                                     | Operating*5      |                      |

| Software watchdog timer                | Operating          |                                                     | Operating        |                      | Stopped            |                                                     | Stopped          |                      |

| Low-voltage<br>detection reset         | Operating          |                                                     | Operating        |                      | Operating          |                                                     | Operating        |                      |

| Other peripheral functions             | Ope                | rating                                              | Operating        |                      | Operating          |                                                     | Operating        |                      |

<sup>\*1:</sup> The main clock runs when the main clock oscillation enable bit in the system clock control register 2 (SYCC2:MOSCE) is set to "1".

<sup>\*2:</sup> The main CR clock or the main CR PLL clock runs when main CR clock oscillation enable bit in the system clock control register 2 (SYCC2:MCRE) is set to "1".

<sup>\*3:</sup> The module runs when the subclock oscillation enable bit in the system clock control register 2 (SYCC2:SOSCE) is set to "1".

<sup>\*4:</sup> The module runs when the sub-CR clock oscillation enable bit in the system clock control register 2 (SYCC2:SCRE) is set to "1".

<sup>\*5:</sup> The hardware watchdog timer stops when the hardware watchdog timer is disabled by the non-volatile register (NVR) interface.

<sup>\*6:</sup> The state of the Flash memory in a standby mode can be selected from two options, normal state and low-power state, by the deep standby mode control bit in the standby control register 2 (STBC2:DSTBYX).

Table 3.1-4 Combinations of Standby Mode and Clock Mode and Internal Operating States (2)

|                                        | Time-ba            | ase timer                                           | Watch            |                      | Stop               |                                                     |                  |                      |  |

|----------------------------------------|--------------------|-----------------------------------------------------|------------------|----------------------|--------------------|-----------------------------------------------------|------------------|----------------------|--|

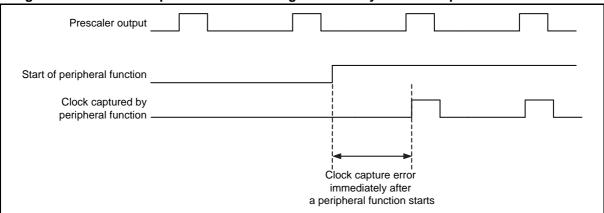

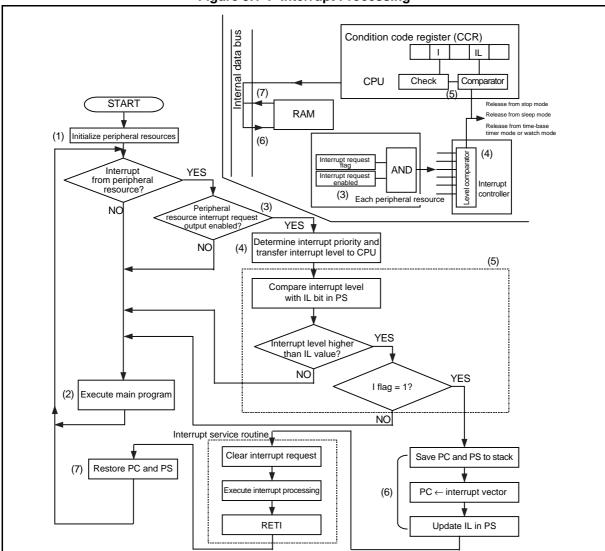

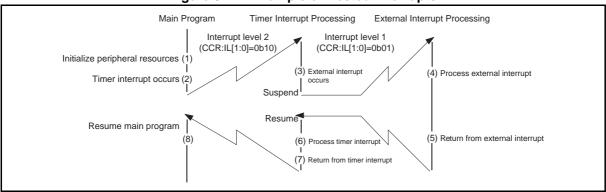

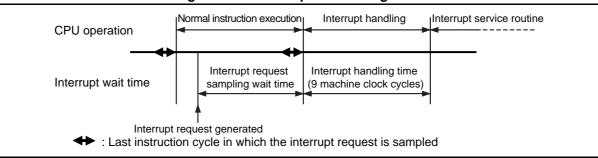

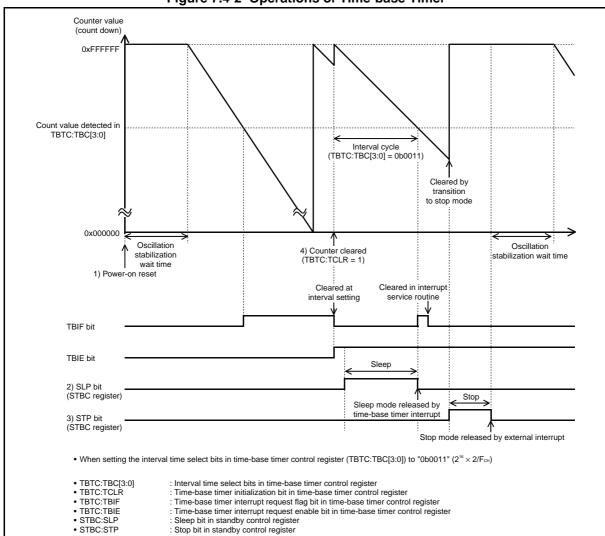

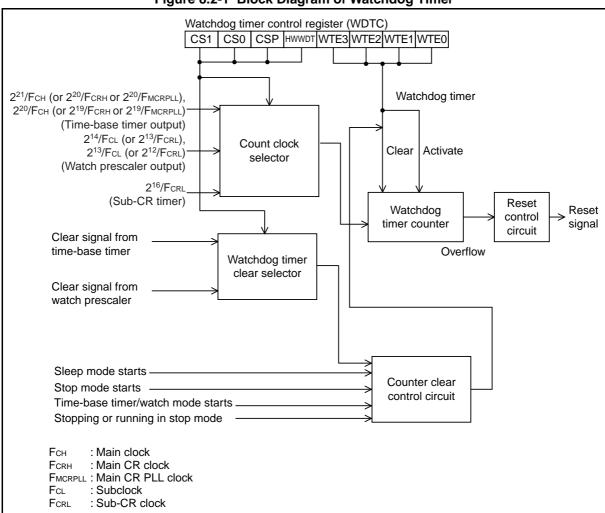

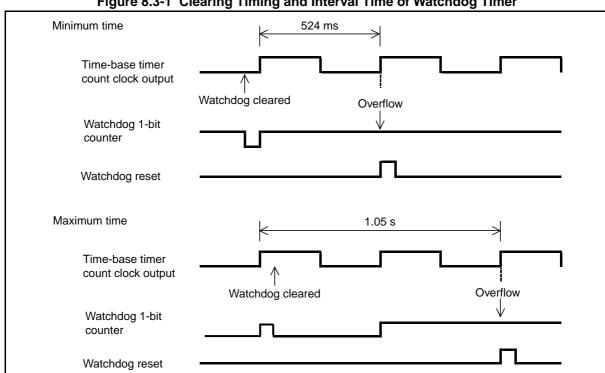

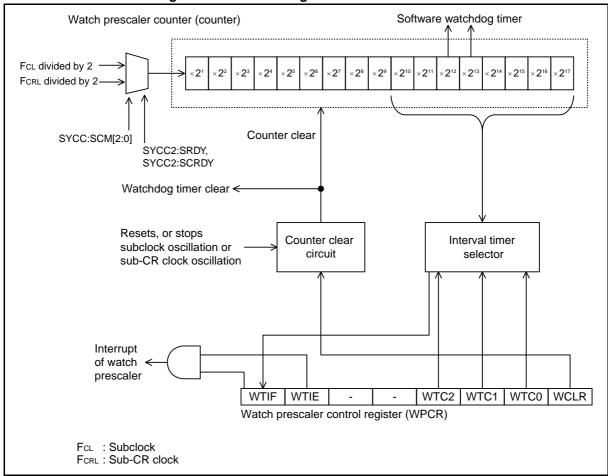

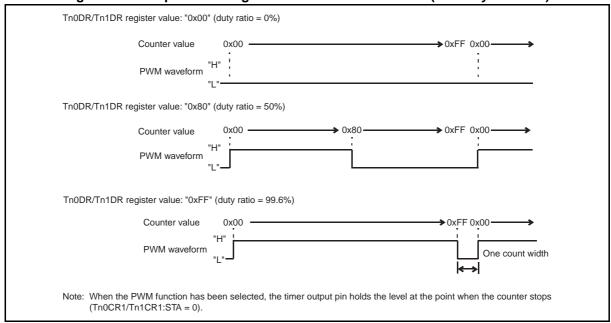

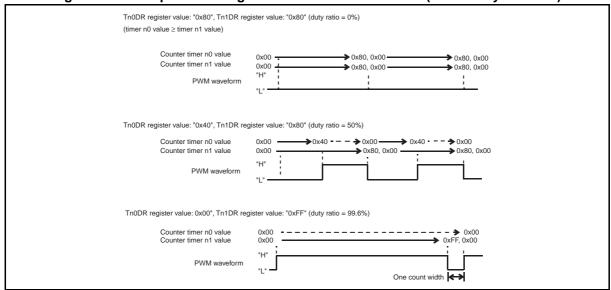

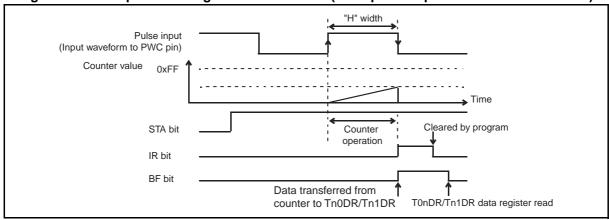

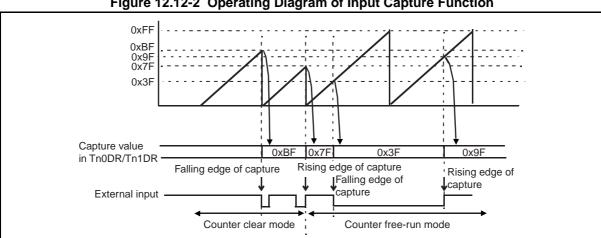

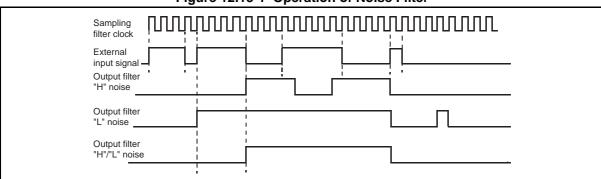

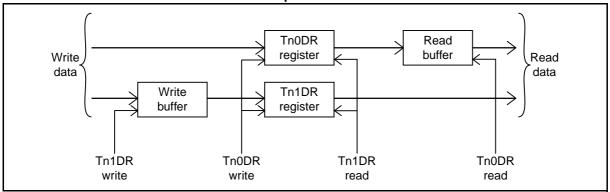

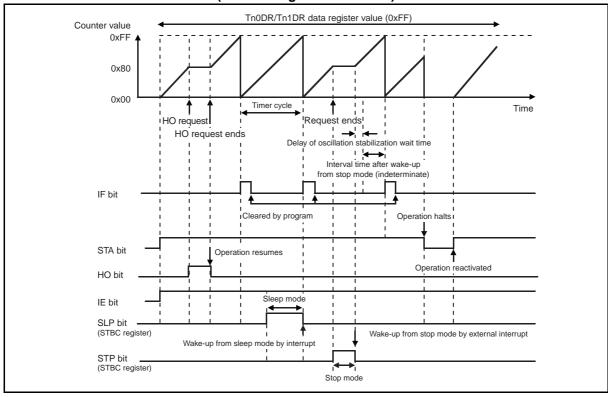

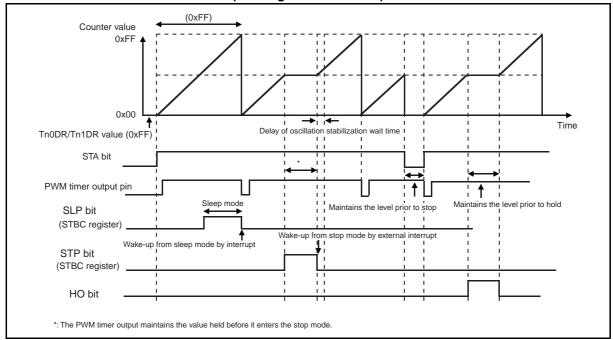

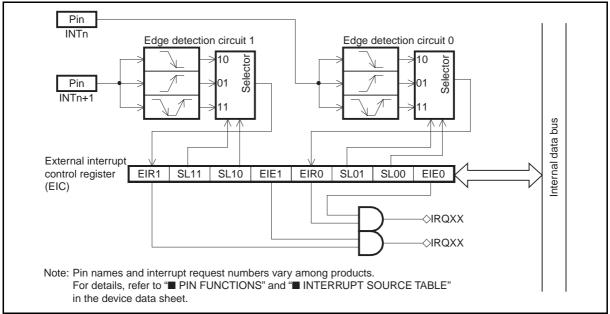

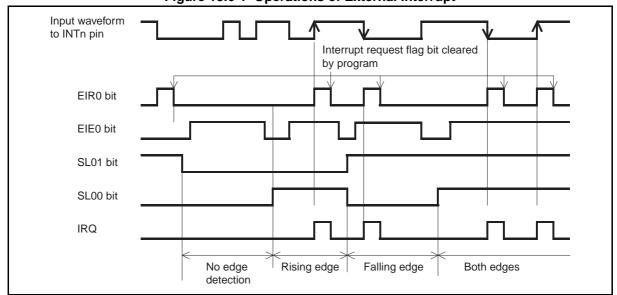

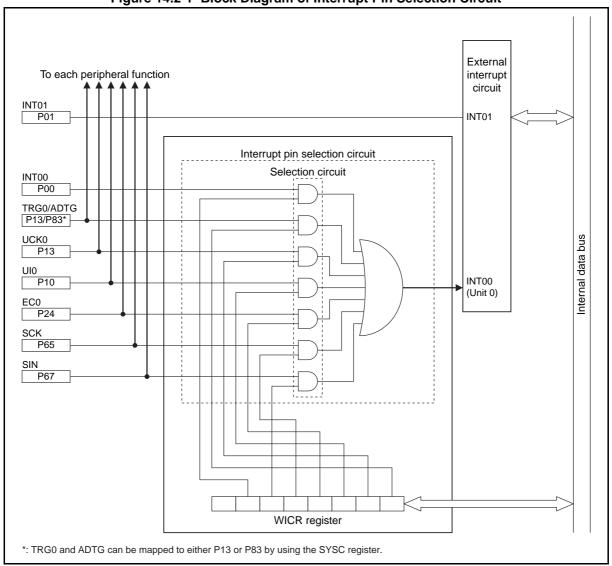

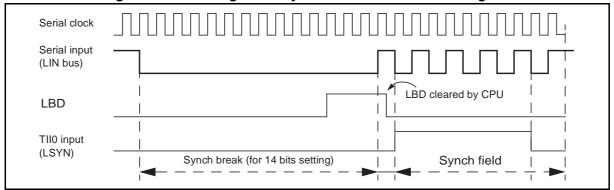

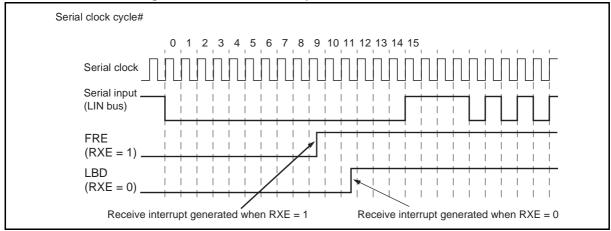

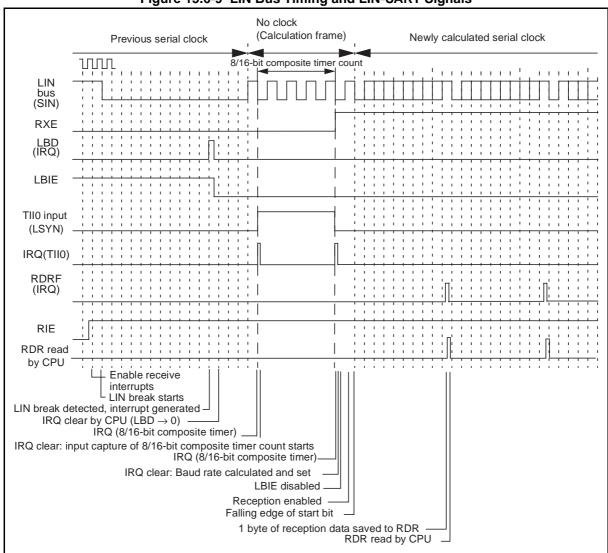

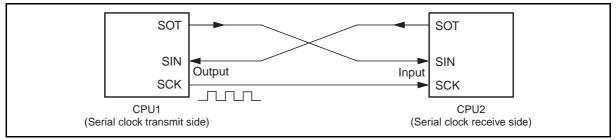

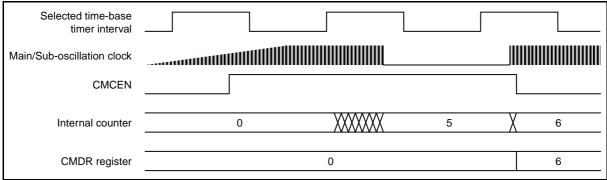

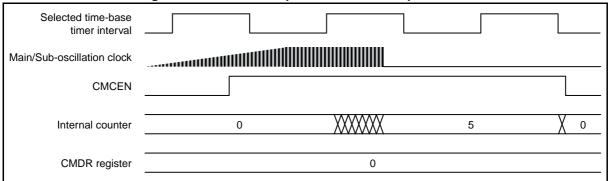

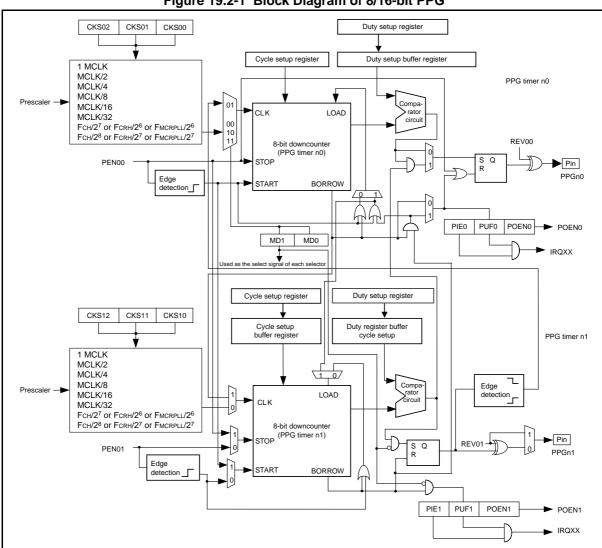

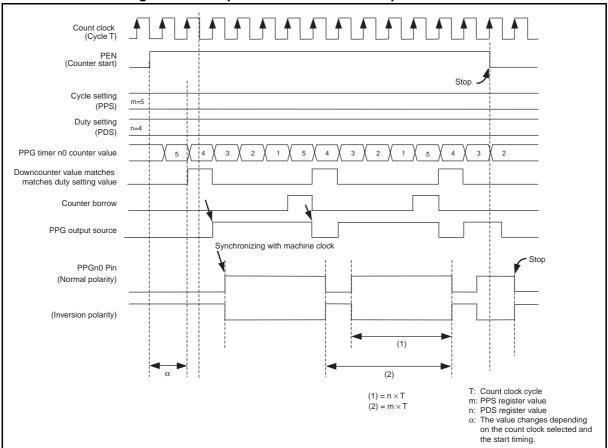

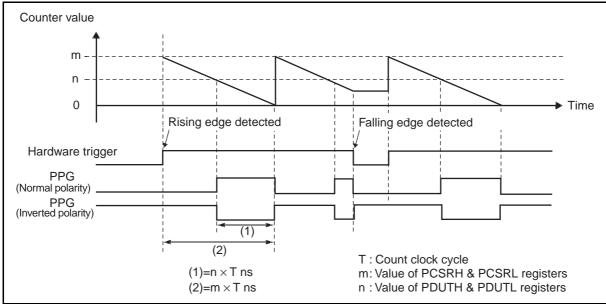

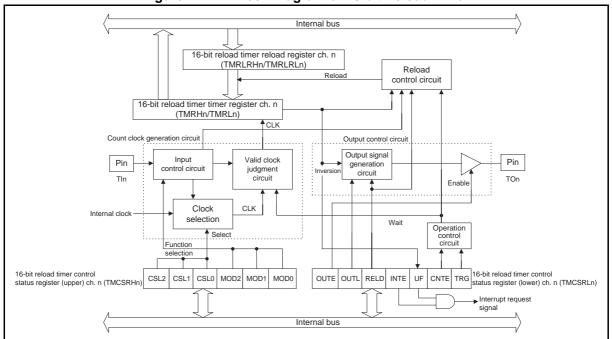

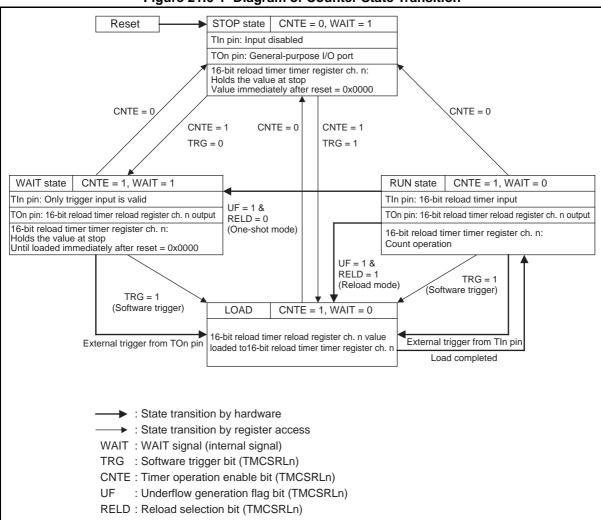

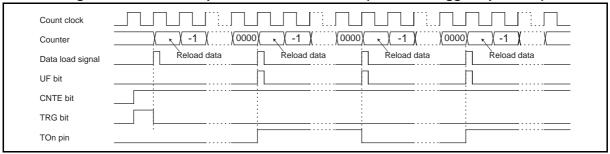

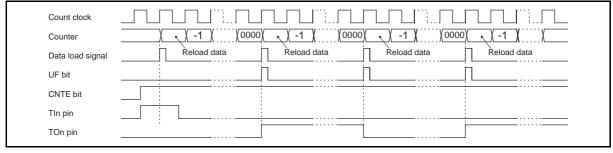

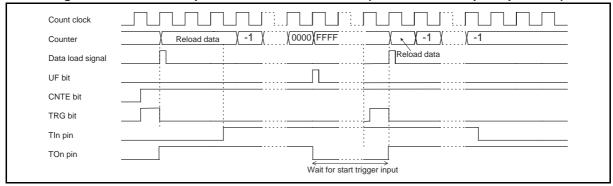

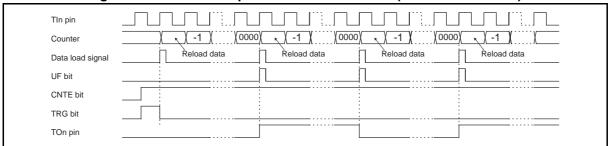

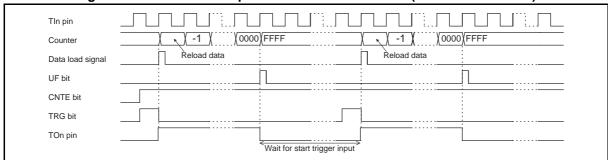

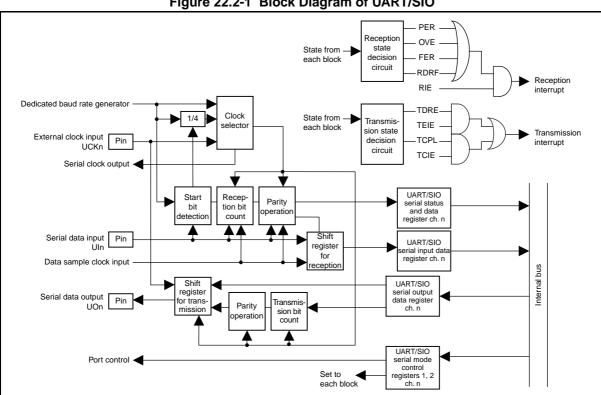

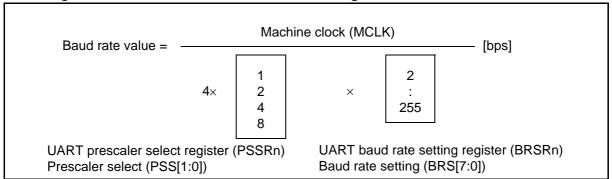

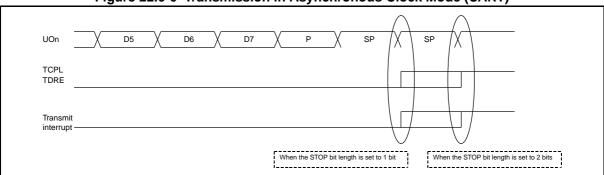

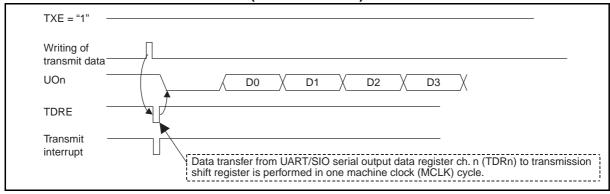

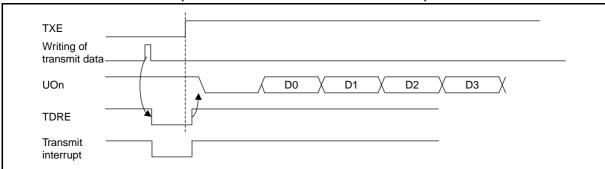

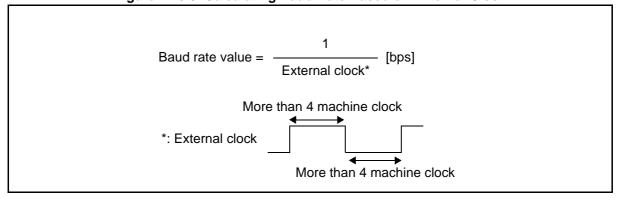

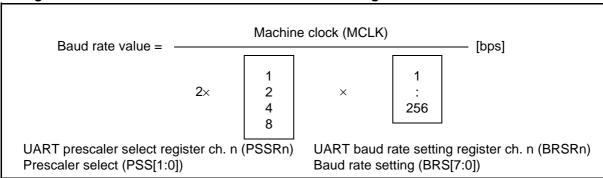

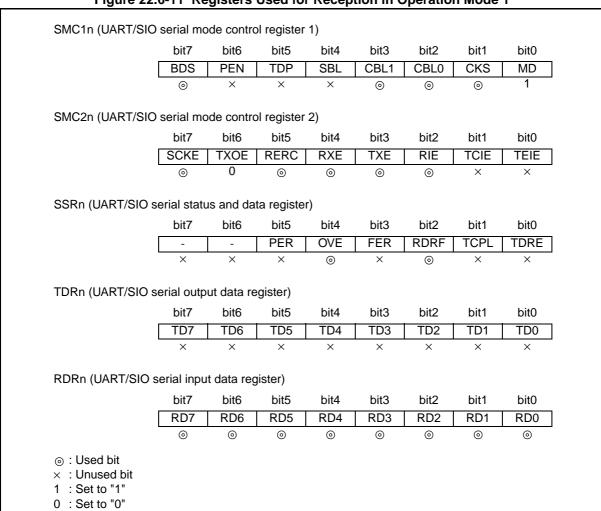

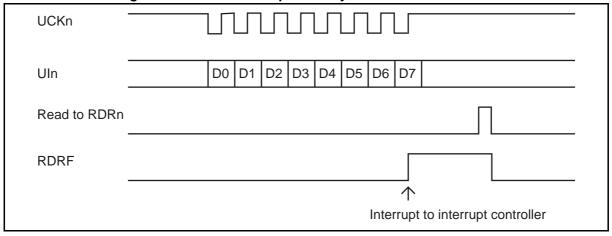

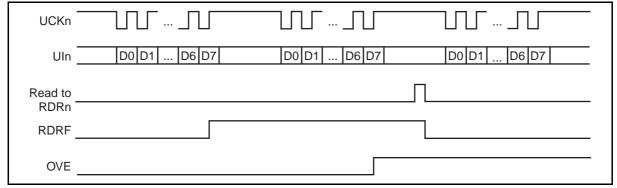

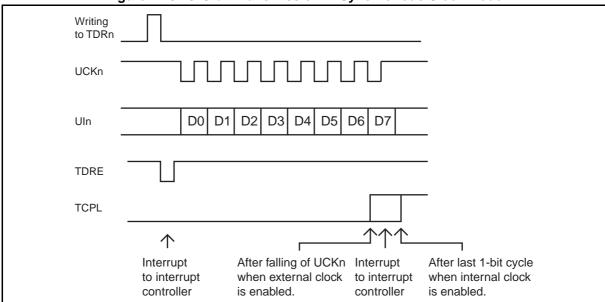

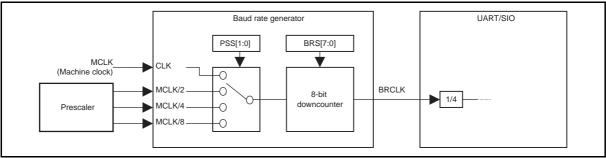

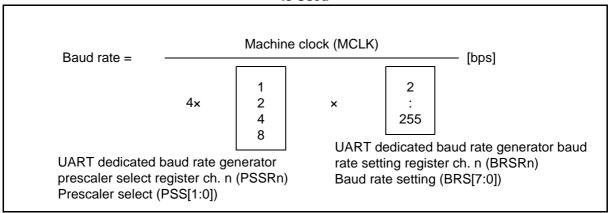

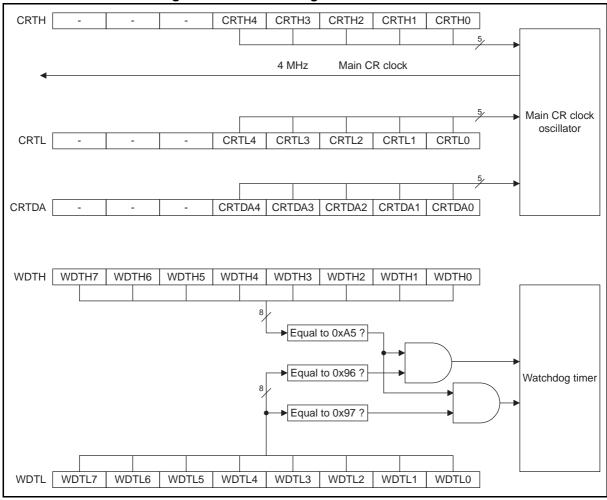

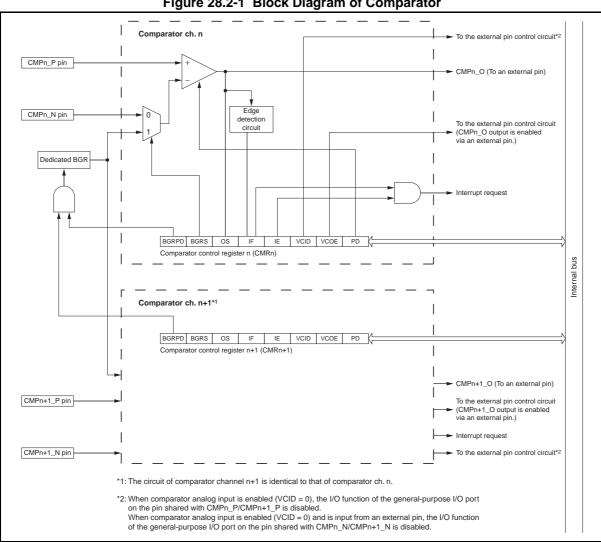

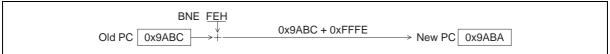

| Function                               | Main clock<br>mode | Main CR<br>clock mode/<br>Main CR PLL<br>clock mode | Subclock<br>mode | Sub-CR<br>clock mode | Main clock<br>mode | Main CR<br>clock mode/<br>Main CR PLL<br>clock mode | Subclock<br>mode | Sub-CR<br>clock mode |  |